您的位置:主页 > 公告动态 > 国王金融动态 > 国王金融动态

英特尔将在三年后打败台积电?

据Anadtech报道,已往几年,英特尔一直在履历公司制造扩张的主要时期。

只管芯片巨头最近在俄亥俄州和德国宣布的新设施引起了许多关注,这是可以明白的——尤其是思量到它们对英特尔的代工服务设计的主要性——但英特尔一直在起劲扩大现有设施以供自己使用。该公司开发下一代 EUV 和 Gate-All-Around 型晶体管 (RibbonFET) 不仅需要确立和完善底层手艺,而且还需要更多空间。

为此,英特尔今天在俄勒冈州为公司的主要开发工厂 D1X 的 Mod3 扩展举行了盛大的开幕式。此次扩建于 2019 年首次宣布,是自 2010 年 D1X 初始建设以来英特尔主要开发工厂的第三次此类 mod (module) 和第二次扩建。

但除了重振旗鼓之外,该工厂的最新模块对英特尔来说是一个真正主要的Mod:它不仅为工厂增添了 270,000 平方英尺的清洁室空间——将 D1X 扩大了约 20%——而且它是唯一的工厂Mod。大到足以支持英特尔将从其 18A 工艺最先使用的高数值孔径 (High NA) EUV 工具——ASML 即将推出的 TWINSCAN EXE:5200 EUV光刻机 ,这个装备比英特尔用于其第一代 EUV 工艺(Intel 4/Intel 3)的 NXE 3000 系列 EUV 装备大得多。它是云云之大,以至于 D1X 的天花板太低而无法容纳机械,更不用说支持其重量的地板了。

因此,可以说Mod3 的构建在很洪水平上是为了这台大型机械。

同时,虽然 D1X-Mod3 直到今天才正式宣布开放,但英特尔自去年 8 月以来已经将要害装备转移到 Mod3中。因此,今天的开幕式是该Mod的正式宣布,由于它的一部门已经设置好(若是尚未使用)。只管云云,凭证英特尔的说法,纵然有了这样的领先优势,该公司预计将在一年内继续使用工具,稀奇是当他们引入剩余的低优先级工具时。

英特尔蹊径图更新:Intel 18A 提前到 2024 年下半年

除了向媒体先容 D1X-Mod3 的开幕式外,英特尔还行使他们最新的新闻宣布会让人人快速领会英特尔开发蹊径图的最新更新。严酷来说,这并不是什么新鲜事——由于所有这些都是在 2 月份的英特尔 2022 年投资者集会上首次宣布了。然则,这是英特尔第一次让手艺媒体而不是投资者来领会其开发事情的现状。

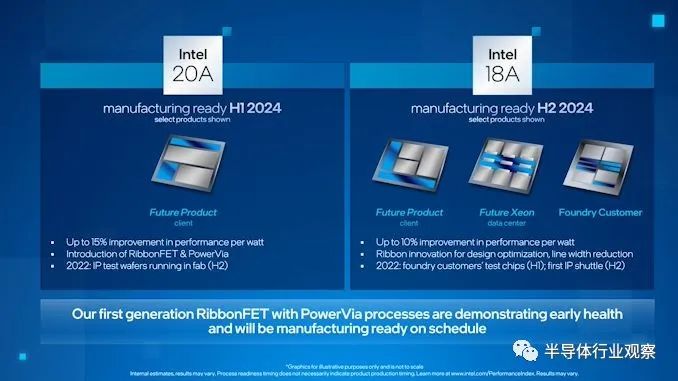

这里的大新闻是英特尔正式提前了在英特尔 18A 节点上制造的最先日期。Intel的第二代“埃”节点原本预计在2025年;但现在该公司将其提高了半年,到 2024 年下半年。

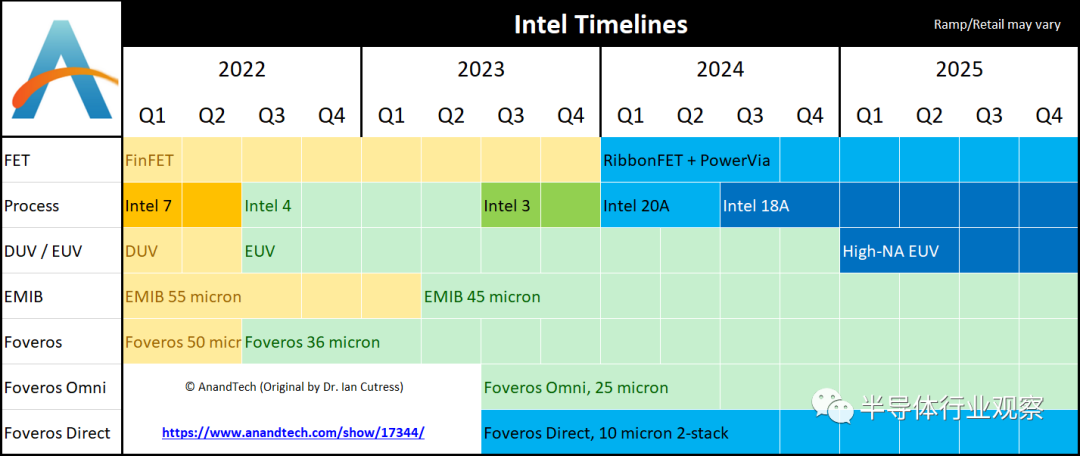

因此,英特尔的蹊径图现在看起来像这样:

由于该公司设计在今年晚些时刻推出其首个 EUV 工艺 Intel 4 做,从 2023 年下半年最先,英特尔的蹊径图最先显得异常紧凑。昔时下半年,Intel 3 将投入生产,这是英特尔的增强的 EUV 工艺。与此同时,Intel 20A 可能会在 6 个月后投入生产。20A 是英特尔的第一个“埃”节点,其中包罗了他们的全栅极型“RibbonFET”FinFets 以及 PowerVias。

然则,若是一切按设计举行,由于 18A 的提前,20A 似乎将是一个相对短暂的节点。英特尔的第二代埃节点,将接纳更新的ribbon设计和对英特尔 GAA 制造手艺的其他改善。由于 18A 仍然是英特尔制造蹊径图中最远的节点,因此该公司对 18A 将带来的所有新事物保持相对缄默,但它仍然是英特尔设计重新确立芯片制造行业无可置疑的向导职位的要害。

据英特尔称,18A 开发希望顺遂,公司的研发营业现在处于或领先于所有开发里程碑,这使公司有信心在 2024 年底而不是 2025 年最先制造基于工艺节点的产物根据最初的设计。

然而,引入 18A 的一个结果是,这意味着英特尔现在一定会在没有所有High NA 机械的情形下最先生产 18A。18A 仍然是High NA 机械首次亮相的工艺节点,但由于 TWINSCAN EXE 5200 预计要到 2025 年才气到位,这意味着英特尔现在必须使用其现有的 3000 系列机械来启动 18A 生产。在这个最新宣布之前,英特尔一直在把High NA 机械和 18A 绑在一起,以是无论这是否总是现真相形,现在显然不是这样。

反过来,这对 18A 生产意味着什么另有待考察。由于英特尔可以将其通俗(非 HA)机械用于 18A,因此High NA 机械的最大优势可能是吞吐量,由于 High NA 更高的精度,英特尔可以处置险些没有(或没有)多重图案的晶圆。看起来,最有可能的效果是英特尔将能够在 2024 年生产 18A,甚至可能量产,但在第一台High NA 机械可用之前,他们将无法进入英特尔规模的大批量生产。

而且,与往常一样,应该注重的是,英特尔的制造蹊径图日期是新工艺节点投入生产的最早日期,而不是基于该手艺的硬件上架的日期。因此,纵然 18A 根据现在的设计在 24 年下半年推出,也很可能在 2025 年的几个月后才气将第一批产物交付客户手中,尤其是若是英特尔在该窗口的后期推出。鉴于这些宣布窗口的伟大规模和英特尔自己的历史,所有这些都是一个可能的赌注,由于英特尔很少在宣布窗口的早期宣布新产物/手艺。

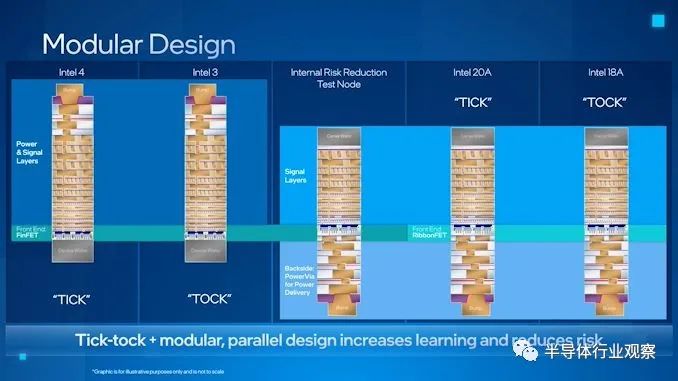

最后,英特尔的开发简报还包罗确认英特尔正在接纳纯内部“降低测试风险”节点作为其 PowerVia 手艺开发流程的一部门。测试节点的目的是通过允许英特尔自力于 RibbonFET 开发和测试 PowerVias 来消除Intel 20A 工艺的所有风险。在这种情形下,测试节点在前端使用英特尔成熟的 FinFET 手艺,同时在后端使用 PowerVia 的测试版本。虽然他们尚未针对 RibbonFET 宣布此类节点,但纵然不存在这样的节点,不也必在 20A 上与 RibbonFET 一起调试第一代 PowerVia 仍然是流程的简化,由于它允许英特尔半自力地追求这两个元素,并在此历程中相互学习。

与英特尔已往开发主要新制造节点的方式相比,这是一个重大转变,甚至他们也是第一个认可这一点的人。英特尔的 10nm 问题在很洪水平上是由于一次将太多的手艺转变捆绑在一起,再加上特征尺寸的异常激进的缩减造成的。将这些器械分成更小、更频仍的制造节点更新是英特尔未来降低这种风险的一种方式。现在有了一个用于 PowerVia 开发的内部测试节点,他们的目的是进一步降低风险,以便能够在 2024 年上半年同时推出 RibbonFET 和 PowerVia,作为英特尔 20A 的一部门。

晶圆厂放缓,英特尔迎来时机

在今年2月的投资集会上,英特尔CEO基辛格在接受台湾经济日报采访的时刻示意,自己的2纳米芯片将在2024年实现量产,这将早于台积电。虽然英特尔信心满满,但英特尔真能实现逾越吗?针对这个论题,semiwiki作者Scotten Jones也揭晓了他的看法。

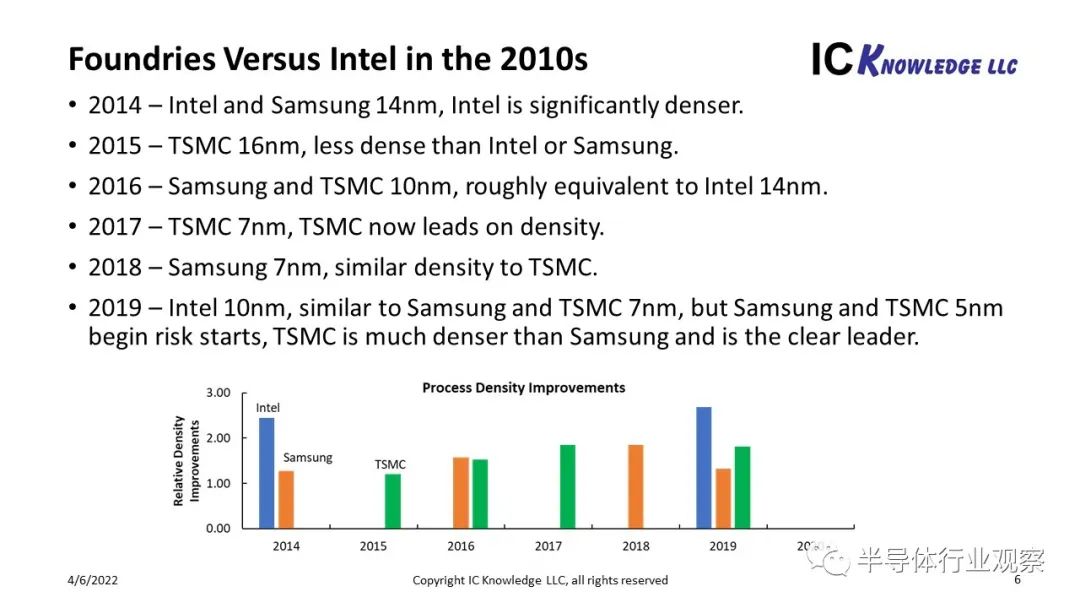

Scotten Jones首先说道,在去年的一个集会上,他曾强调,台积电是当之无愧的向导者。在那次集会之后,经常有人问他——英特尔什么时刻会遇上台积电。那时作者的回覆是——除非台积电自毁长城,否则永远不会。

但Scotten Jones示意,在一年后,代工厂最先有点步履蹒跚,但英特尔正在加速,现在的英特尔是否能遇上呢?在提出了新的设想后,Scotten Jones回首了一些英特尔的历史,讨论了他们在 2000 年月的向导职位,然后说到 2010 年月他们是怎么最先落伍的。

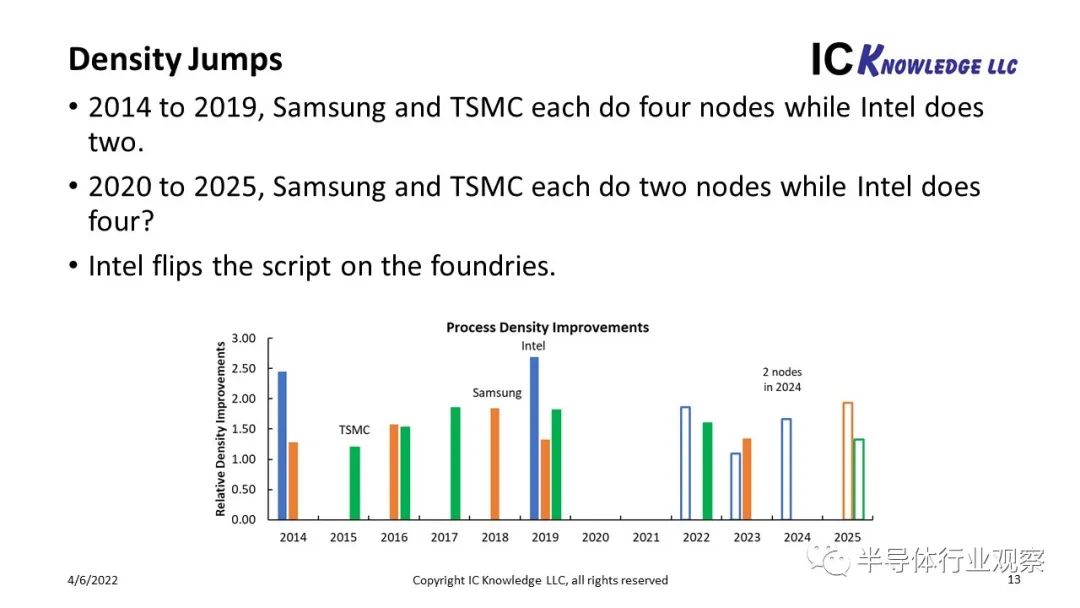

据先容,在2014 年至 2019年间,三星和台积电各推出 4 个节点,但英特尔推出 2 个,这主要是由于英特尔节点的单个密度跳跃更大,但当你将 4 个代工厂跳跃链接在一起时,它们的密度增添跨越英特尔并处于领先职位。图 7总结了这一点。

上图仅说明晰英特尔的“节点”,它们并没有阻滞不前,对于 14nm,他们宣布了 5 个版本,所有版本都具有相同的密度,但性能逐渐提高;对于 10nm,他们宣布了 4 个版本,再次以相同的密度但有所提高性能(注重最后一个版本现在已重命名为 7nm)。

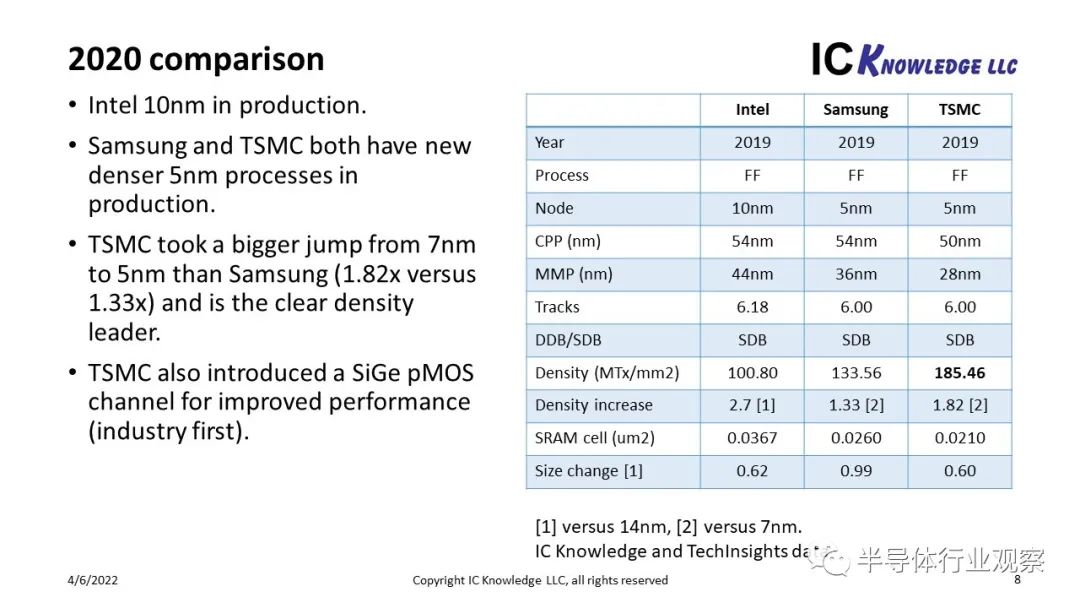

到 2020 年,三星和台积电都在生产 5nm,与英特尔同期的10nm 相比,它们的工艺更麋集。台积电从 7nm 跃升到 5nm,然后是三星,而且依附最麋集的工艺、最小的 SRAM 单元尺寸和业界首个硅锗 FinFET 成为显著的向导者。图 8总结了这一点。

但到了 2021 年,晶圆厂的生长速率放缓,事态似乎最先转变。

Scotten Jones在文章中指出,三星 3nm 在这年遇到了良率问题,但他坚信,到 2022 年,三星的 3GAE(早期)工艺将险些专门用于内部产物,2023 年将向外部客户宣布 3GAP(性能)。三星选择了 3nm 水平纳米片(HNS) (三星称为 Multibridge 的一种GAA工艺)。我信托 HNS 生产问题仍在解决中,三星对率先使用 HNS 的兴趣导致了延误和低良率。

台积电确实冒着在 2021 年最先使用基于 FinFET 的 3nm 工艺的风险,但现在生产推迟到 2022 年终,并在 2023 年推出行业产物。2019 年,台积电有风险试产 5nm ,到 2020 年终,搭载台积电 5nm 工艺芯片iPhone亮相,用 3nm芯片的iPhone我们要到 2023 年才气看到。台积电还将这一工艺的密度从最初的 1.7 倍目的降低到约 1.6 倍,同时降低了性能目的。

在三星和台积电履历延迟的同时,英特尔宣布了“Intel Accelerated”,这是一个在 4 年内实现 4 个节点的激进蹊径图。思量到 14nm 用了 3 年而 10nm 用了 5 年,这确实加速了。坦率地说,当它宣布时我对此持嫌疑态度,但在最近的投资者流动中,英特尔宣布,将最先进的Intel 18A容易从预期的 2025 年提前到 2024 年,这让我尤为惊讶。

2025年,会是一个转折点吗?

根据英特尔最新的蹊径图,他们的工艺会根据以下时间推出:

2022年,英特尔将推出 4nm 工艺,这是英特尔首次使用 EUV装备,新工艺的性能将比 7nm 提升 20%。英特尔之前曾谈到这一代的密度提高了 2 倍,但现在只是说“显著的密度提高”,我们估量为 1.8 倍。

三星 3nm 可能仅用于内部使用,密度提高 1.35 倍,在相同功率下性能提高 35%,在相同性能下功率降低 50%。其密度改善不是很令人印象深刻,但性能和功率改善可能是由于接纳了HNS手艺。TSMC 3nm 基于 FinFET,将提供约 1.6 倍的密度改善,在相同功率下性能提高 10%,在相同性能下功率降低 25%。

2023年,英特尔将推出3nm 工艺,性能提升 18%,库更麋集,EUV 使用更多。我们估量密度提高了 1.09 倍,使其更像是一个半节点。三星 3GAP 应该可供外部客户使用,台积电 3nm 部件应该泛起在 iPhone 中。

2024 年上半年英特尔的Intel 20A(20 埃 = 2nm)工艺将亮相,新节点将带来 15% 的性能提升。这将是英特尔的第一个 HNS(他们称之为 RibbonFET),他们还将引入后头供电(他们称之为 PowerVia)。后头供电解决了 IR 功率下降问题,同时使前端互连更容易。我们估量,这个工艺的密度较之上一代提高了 1.6 倍。

2024 年下半年,Intel 18A 工艺将提前到来,并带来 10% 的性能提升。我们估量密度提高了 1.06 倍,使这又是一个半节点。这个历程已经从 2025 年最先,英特尔示意他们已经向客户交付了测试装备。

2025年下半年,三星 2nm 将亮相,我们预计它将是 HNS,由于它将是三星的第三代 HNS(将 3GAE 算作第一代,GAP算作第二代),而他们的前几代密度提升相对较少,将有我们展望 1.9 倍。

台积电尚未宣布他们的 2nm 工艺,只是说他们希望在 2025 年拥有最好的工艺。我们可能会在 2024 年看到 他们2nm,但现在我们将其放在 2025 年,我们预计同样使用HNS 工艺,而且估量密度为 1.33 倍改善。我们信托密度的提升将是适度的,由于它是台积电的第一个 HNS,而且由于 3nm 工艺异常麋集,进一步的改善将加倍难题。

此图说明晰英特尔若何通过做 4 个节点而代工厂做 2 个节点来在代工厂上“翻转剧本”。

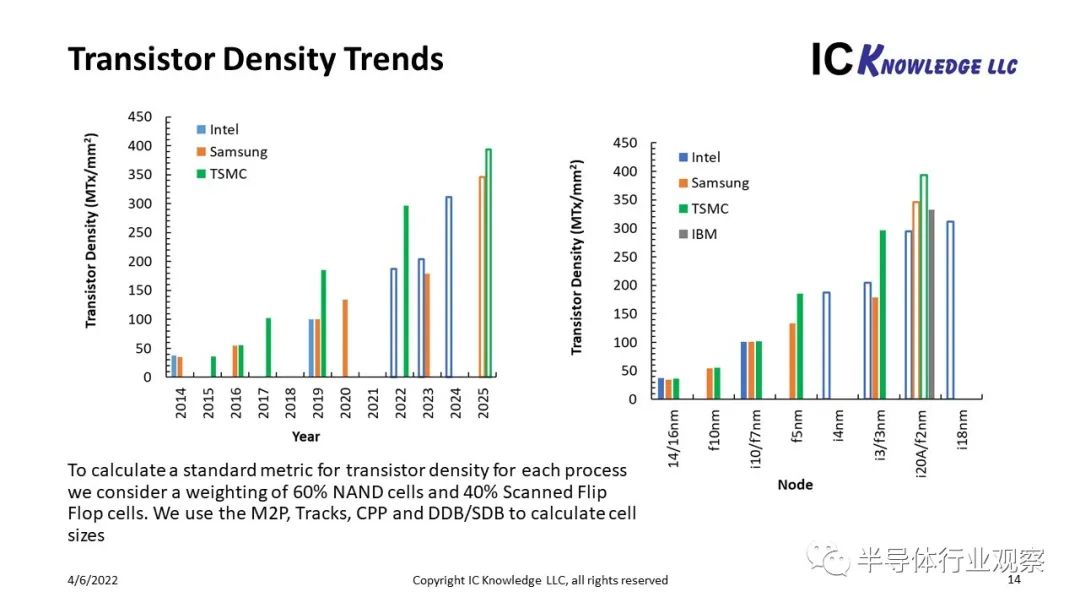

我们现在可以看看英特尔、三星和台积电到 2025 年的密度对照。我们还凭证他们的 2nm 通告添加了 IBM 的 2nm 研究装备。下图显示了密度与年份和节点的关系。

往后图来看,我们预计台积电将在 2025 年之前保持密度领先。

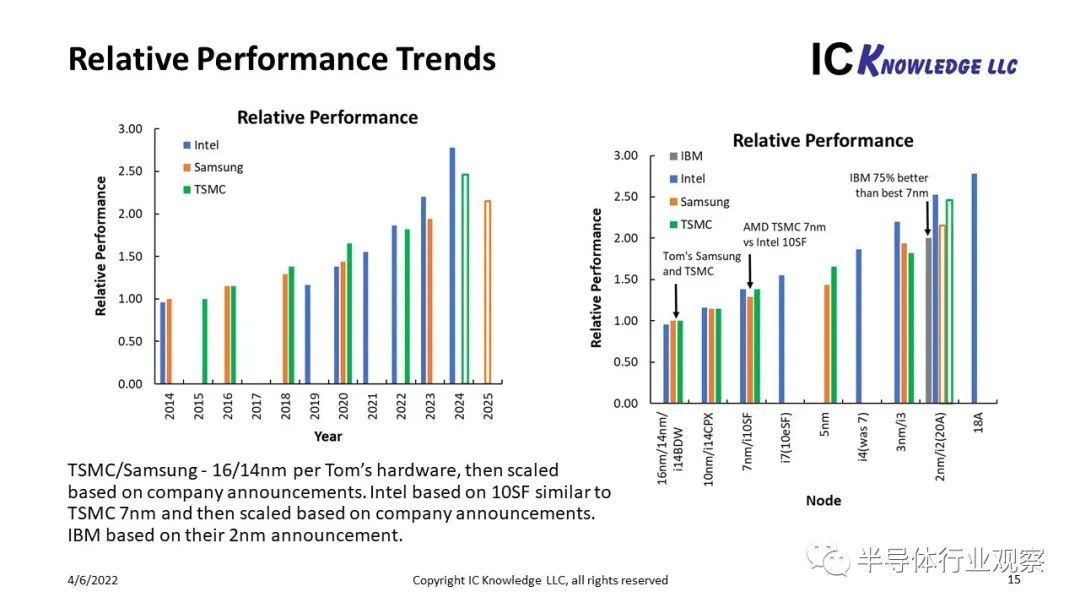

若是没有在差其余制程上运行相同的设计,就很难将历程相互对照以获得性能,而且这种情形很少发生。我们天生此图的方式如下:

Apple A9 在三星 14nm 和台积电 16nm 上举行生产,Tom’s hardware 发现两个版本的性能相同,我们已将此节点的性能尺度化为三星和台积电的 1。

从 14/16nm 节点到 3nm,我们使用了公司宣布的性能改善来绘制相对性能。对于 2nm,我们使用了我们自己的展望。

我们没有任何在英特尔工艺以及三星或台积电上运行的设计。然则,AMD 和 Intel 都生产 X86 微处置器,而 AMD 接纳 TSMC 7nm 工艺的微处置器已经与具有相似性能的 Intel 10nm Superfin 处置器竞争,我们将 Intel 10SF 设置为与 TSMC 7nm 相同的性能。这并不理想,假设两家公司在设计方面都做得同样精彩,但却是最好的对照。然后,我们凭证英特尔的通告从 10SF 扩展了所有其他英特尔节点。

再一次,我们凭证 IBM 的 2nm 通告将 IBM 的 2nm 放在了这张图表上。

我们的剖析使我们信托,英特尔可能会在一年和节点的基础上取得性能领先。这与英特尔宣称的“每瓦性能领先”的目的是一致的。假设台积电指的是密度,他们声称他们将在 2025 年拥有最佳工艺的说法也可能是准确的。

总之,我们信托英特尔能够在代工厂陷入逆境的时刻显著加速他们的工艺开发。只管我们预计英特尔不会在所研究的时间段内重新获得密度领先优势,但我们确实信托他们可以重新夺回性能领先优势。

到 2022 年底,当我们看到英特尔 4nm 是否认时问世时,我们应该会再次获得有关希望的好新闻。

参考链接: