您的位置:主页 > 公告动态 > 国王金融动态 > 国王金融动态

一种罕有创新的AI芯片

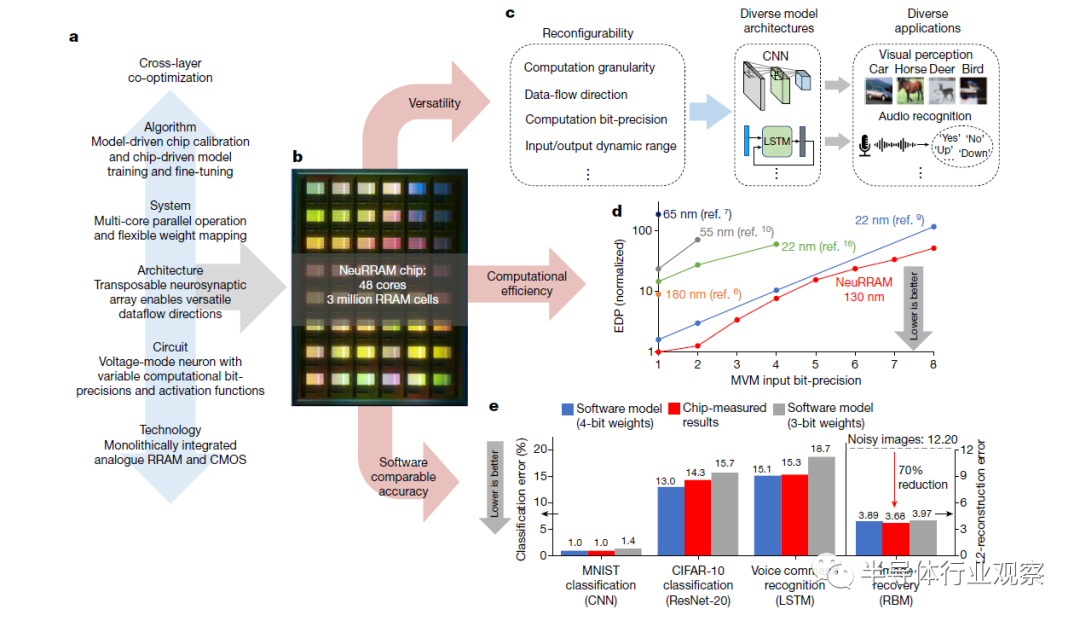

直接在边缘装备上实现日益庞大的人工智能 (AI) 功效需要*的边缘硬件能效。基于电阻式随机存取存储器 (RRAM) 的存内盘算 (CIM) 有望通过将 AI 模子权重存储在麋集、模拟和非易失性 RRAM 装备中,并通过直接在 RRAM 中执行 AI 盘算来知足这种需求,从而消除在单独的盘算和内存之间举行高能耗的数据移动。只管最近的研究已经展示了完全集成的 RRAM-CIM 硬件上的内存矩阵向量乘法,但 RRAM-CIM 芯片的目的仍然是同时提供高能效、支持种种模子的多功效性和软件可比的精度。只管效率、多功效性和准确性对于普遍接纳该手艺都是必不能少的,但它们之间相互关联的权衡不能通过单独改善随便抽象层的设计来解决。在这里,通过对从算法和架构到电路和装备的所有设计条理举行配合优化,我们展示了 NeuRRAM——一种基于 RRAM 的 CIM 芯片,它同时提供了为差异模子架构重新设置 CIM 内核的多功效性,能效到达在种种盘算位精度上比以前*进的 RRAM-CIM 芯片好 1 倍,在种种 AI 义务中推理精度可与量化为4比特权重的软件模子相媲美,在MNIST数据集分类上准确度 在 99.0% 以及在 CIFAR-10 图像分类准确度为 85.7% ;在谷歌语音下令识其余准确率为 84.7%;在贝叶斯图像恢复义务中图像重修错误削减了 70%。

电阻随机存取存储器 (RRAM) 存内盘算 (CIM) 领域的早期研究着重于在制造的 RRAM 装备上展示人工智能 (AI) 功效,同时使用片外软件和硬件来实现基本功效,例如一个完整系统中的模数转换和神经元激活。只管这些研究提出了种种手艺来减轻与模拟相关的硬件非理想性对推理准确性的影响,但所讲述的 AI 基准测试效果通常是通过对特征装备的数据举行软件仿真获得的。由于硬件非理想模子的不完整建模,与完全硬件丈量的效果相比,这种方式通常会高估准确度。

最近的研究注释,完全集成的 RRAM 互补金属氧化物半导体( CMOS) 芯片可以执行内存中矩阵向量乘法 (MVM)。然而,要在现实 AI 应用中普遍接纳 RRAM-CIM 芯片,它需要同时提供高能效、支持种种 AI 模子架构的天真性和软件可比的推理精度。到现在为止,还没有一项旨在同时改善所有这三个方面设计的研究。此外,先前研究中的人工智能应用级基准测试的多样性和庞大性是有限的。没有一项研究通过实验丈量了多个边缘 AI 应用程序,其庞大性与 MLPerf Tiny 中的应用程序相匹配(MLPerf Tiny 是边缘 AI 硬件的常用基准测试套件)。挑战来自效率、天真性和准确性之间相互关联的权衡。RRAM-CIM 架构中的高度并行模拟盘算带来了*的效率,但难以实现与数字电路相同水平的功效天真性和盘算精度。同时,由于在边缘使用较少的过分参数化模子,对于更庞大的 AI 义务,实现对硬件非理想的算法弹性变得加倍难题。

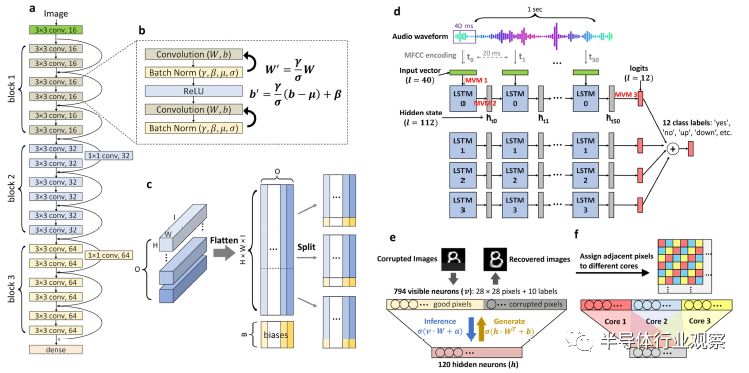

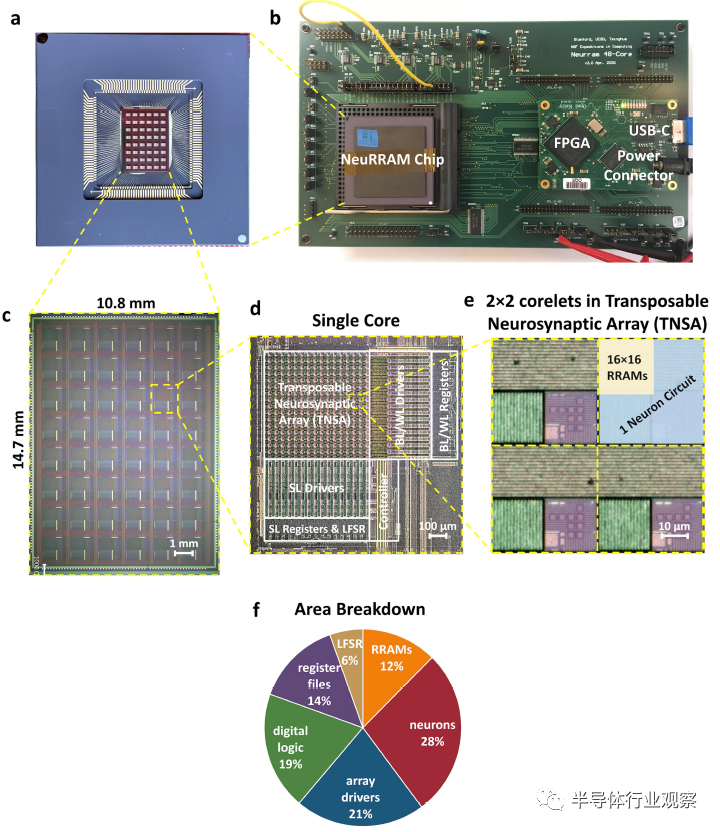

为了应对这些挑战,我们展示了NeuRRAM ,这是一种 48 核 RRAM-CIM 硬件,涵盖了整个设计栈中的创新。(1)在器件层面,单片集成了300万个具有高模拟可编程性的RRAM器件与CMOS电路。(2) 在电路层面,电压模式神经元电路支持可变盘算位精度和激活函数,同时以低功耗和紧凑的面积举行模数转换。(3) 在架构层面,双向可调神经突触阵列 ( TNSA ) 架构能够以最小的面积和能量开销实现数据流偏向的可重构性。(4)在系统层面,48个CIM焦点可以并行举行推理,支持多种权重映射计谋。(5) 最后,在算法层面,种种硬件算法协同优化手艺减轻了硬件非理想对推理精度的影响。我们展示了一系列 AI 义务的完全硬件丈量推理效果,使用包罗卷积神经网络 (CNN) 、是非时影象网络(LSTM)和概率图形模子(图1e) 在内的种种 AI 模子测试 CIFAR-10 和 MNIST 数据集的图像分类、Google 语音下令识别和 MNIST 图像恢复。该芯片经由丈量可实现比以前*进的 RRAM-CIM 芯片更低的能量延迟积 (EDP),同时它可以在一系列设置上运行以顺应种种 AI 基准应用程序(图 1d)。

图 1 | NeuRRAM芯片的设计方式和主要孝顺。

a ,整个设计栈的跨层协同优化使NeuRRAM能够同时提供高通用性、盘算效率和软件可比的推理精度。b , NeuRRAM芯片的显微图。c ,设计各个方面的可重构性使NeuRRAM能够为种种应用实现差其余 AI 模子。d ,EDP 的对照,这是最近基于 RRAM 的 CIM 硬件中常用的能效和性能指标。e ,在NeuRRAM上完全硬件丈量的推理精度可与种种 AI 基准测试中量化为 4 位权重的软件模子相媲美。

可重构 RRAM-CIM 架构

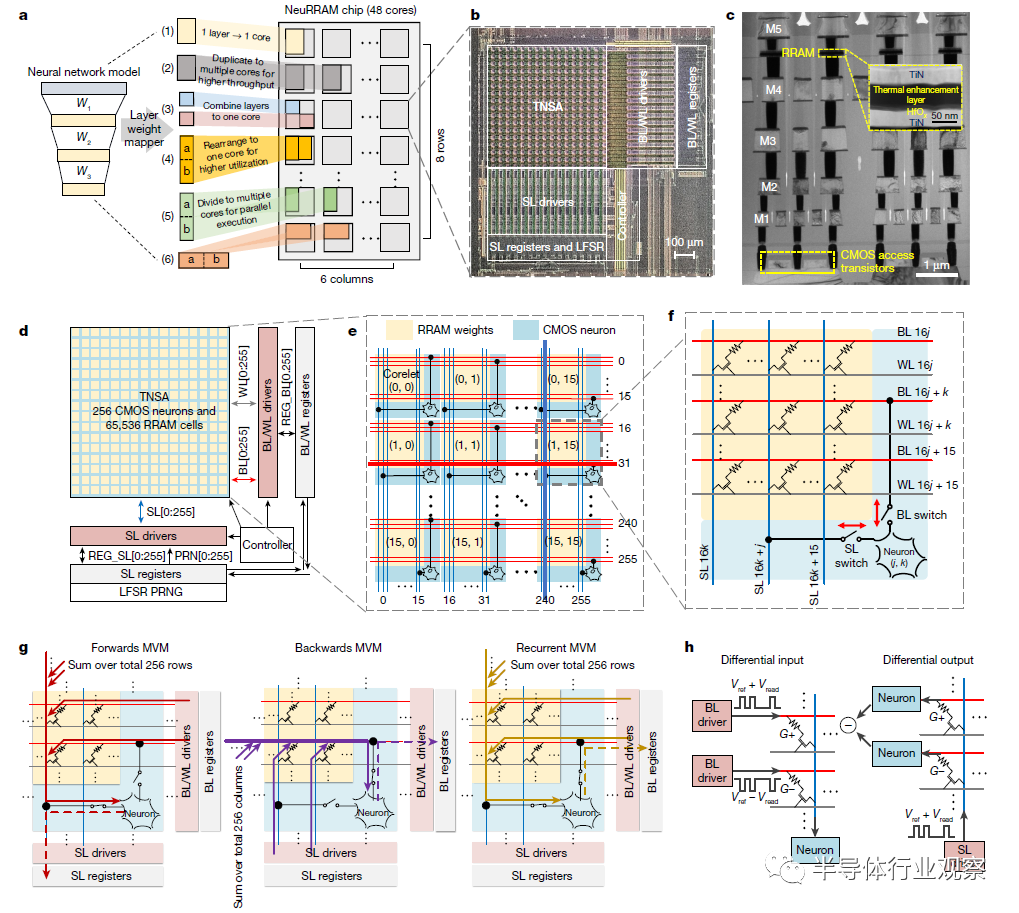

一个 NeuRRAM 芯片由 48 个可以并行执行盘算的 CIM 内核组成。内核可以在不使用时通过电源门控有选择地关闭,而模子权重由非易失性 RRAM 装备保留。每个内核的焦点是一个 TNSA,由 256 × 256 RRAM 单元和 256 个 CMOS 神经元电路组成,用于实现模数转换器 (ADC) 和激活功效。沿边缘的附加外围电路提供推理控制并治理 RRAM 编程。

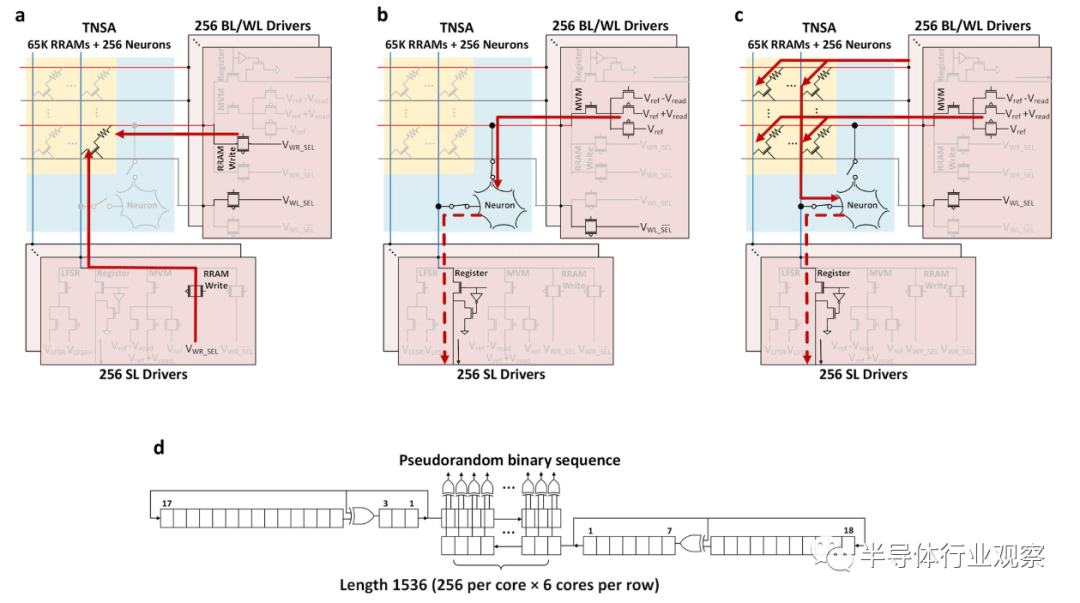

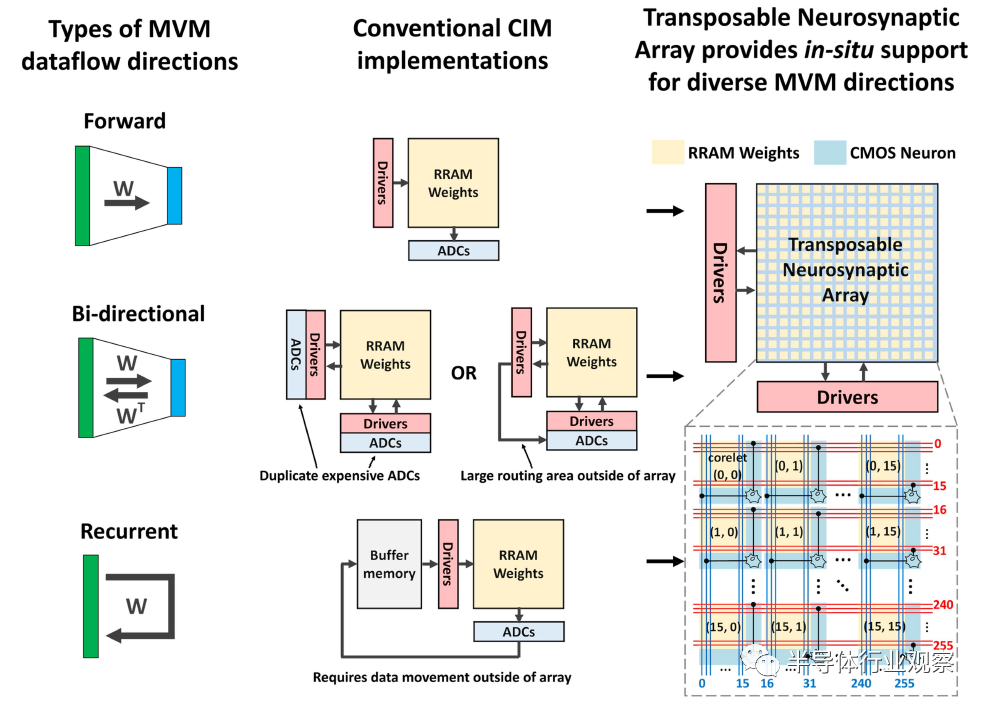

TNSA 架构旨在提供对数据流偏向的天真控制,这对于启用具有差异数据流模式的差异模子架构至关主要。例如,在通常应用于视觉相关义务的 CNN 网络中,数据以单一偏向流过差异层,以天生差异抽象级其余数据示意;在用于处置时间数据(如音频信号)的 LSTM网络 中,数据在多个时间步长内频频通过统一层;在诸如受限玻尔兹曼机 (RBM) 等概率图模子中,概率采样在层之间往返执行,直到网络收敛到高概率状态。除了推理之外,多个 AI 模子的梯度下降训练时代的误差反向流传需要反转通过网络的数据流偏向。

然而,传统的 RRAM-CIM 架构仅限于通过将 RRAM 交织阵列的行和列硬连线到外围的专用电路来驱动输入和丈量输出,从而在单一偏向上执行 MVM。一些研究通过添加分外的硬件来实现可重新设置的数据流偏向,这会导致大量的能量、延迟和面积损失(扩展数据图 2)如:执行双向(前向和后向)数据流需要在两头部署许多重复的耗电且占用面积的 ADC RRAM 阵列 或将大面积区域用于将阵列的行和列路由到共享数据转换器;循环毗邻需要将输出写入 RRAM 阵列外部的缓冲存储器,并将它们读回以举行下一个时间步盘算。

TNSA 架构以很少的开销实现了动态数据流可重构性。而在传统设计中,诸如 ADC 的 CMOS 外围电路仅毗邻在 RRAM 阵列的一端,而 TNSA 架构在物理上将 RRAM 权重和 CMOS 神经元电路交织,并沿行和列的长度将它们毗邻起来。如图 2e 所示,TNSA 由 16 × 16 个这样的交织小核(corelet)组成,这些小核由共享位线 (BL) 和沿水平偏向的字线 (WL) 和沿垂直偏向的源极线 (SL) 毗邻偏向。每个 corelet 包罗 16 × 16 RRAM 装备和一个神经元电路。神经元毗邻到 16 个 BL 和通过 corelet 的 16 个 SL 中的 1 个 BL 和 1 个 SL,并卖力整合来自毗邻到统一 BL 或 SL 的所有 256 个 RRAM 的输入。这些 RRAM 中有 16 个与神经元在统一个 corelet 中;其他 240 个在沿统一行或列的其他 15 个小核内。详细来说,图 2f 显示了 corelet ( i , j ) 中的神经元毗邻到第 (16 i j ) 个 BL 和第 (16 j i ) 个 SL。这种设置确保每个 BL 或 SL *地毗邻到一个神经元,同时这样做不会使阵列两头的神经元重复,从而节约面积和能量。

图 2 | NeuRRAM 芯片的可重构架构。

a ,NeuRRAM 芯片的多核架构,以及符号为 (1) 到 (6) 的种种方式,用于将神经网络层映射到 CIM 内核。b ,单个 CIM 内核上的放大芯片显微照片。c ,横截面透射电子显微镜图像,显示了单片集成 RRAM 和 CMOS 的层堆叠。d ,CIM焦点的框图。内核由 TNSA、BL、WL 和 SL 的驱动程序、存储 MVM 输入和输出的寄存器、LFSR 伪随机数发生器 (PRNG) 和控制器组成。在 MVM 输入阶段,驱动器将寄存器输入 (REG) 和 PRNG 输入 (PRN) 转换为模拟电压并将它们发送到 TNSA;在 MVM 输出阶段,驱动器未来自神经元的数字输出通过 REG 通报回寄存器。e ,TNSA 的架构由 16 × 16 的 corelet 组成,具有交织的 RRAM 权重和 CMOS 神经元。每个神经元集成来自毗邻到相同水平 BL 或垂直 SL 的 256 个 RRAM 的输入。f ,每个 corelet 包罗 16 × 16 RRAM 和 1 个神经元。神经元毗邻到通过 corelet 的 16 个 BL 中的 1 个和 16 个 SL 中的 1 个,而且可以将 BL 和 SL 用于其输入和输出。g ,TNSA可以在前向、后向或循环偏向上为MVM动态设置。h ,差分输入和差分输出方案,用于在前向和后向 MVM 时代实现实值权重。权重被编码为相邻行(G 和 G-)上两个 RRAM 单元之间的差分电导。

此外,神经元将其 BL 和 SL 开关用于其输入和输出:它不仅通过开关吸收来自 BL 或 SL 的模拟 MVM 输出,还通过相同的开关将转换后的数字效果发送到外围寄存器。通过设置在神经元的输入和输出阶段使用哪个开关,我们可以实现种种 MVM 数据流偏向。图 2g 显示了 TNSA 启用的前向、后向和循环 MVM。为了实现前向 MVM(BL 到 SL),在输入阶段,输入脉冲通过 BL 驱动器施加到 BL,由 RRAM 加权并通过其 SL 开关进着迷经元;在输出阶段,神经元通过其 SL 开关将转换后的数字输出发送到 SL 寄存器;为了实现循环 MVM(BL 到 BL),神经元通过其 SL 开关吸收输入,并通过其 BL 开关将数字输出发送回 BL 寄存器。

大多数 AI 模子的权重都取正值和负值。我们将每个权重编码为沿统一列的相邻行上的两个 RRAM 单元之间的电导差(图 2h)。正向 MVM 使用差分输入方案执行,其中 BL 驱动器将具有相反极性的输入电压脉冲发送到相邻的 BL。反向 MVM 使用差分输出方案执行,在神经元完成模数转换后,我们以数字方式减去毗邻到相邻 BL 的神经元的输出。

为了*限度地提高 48 个 CIM 内核上 AI 推理的吞吐量,我们实行了普遍的权重映射计谋选择,使我们能够通过多核并行 MVM 同时行使模子并行性和数据并行性(图 2a)。以 CNN 网络为例,为了*化数据并行性,我们将盘算最麋集的层(早期卷积层)的权重复制到多个焦点,以对多个数据举行并行推理;为了*化模子并行性,我们将差其余卷积层映射到差其余焦点,并以流水线方式执行并行推理。同时,我们将权重维度跨越 RRAM 数组巨细的层划分为多个段,并将它们分配给多个内核以并行执行。方式中提供了对权重映射计谋的更详细形貌。中央数据缓冲器和部门和累加器由与 NeuRRAM 芯片集成在统一块板上的现场可编程门阵列 (FPGA) 实现。只管这些数字外设模块不是本研究的重点,但它们最终需要集成在统一芯片中的生产停当 RRAM-CIM 硬件中。

高效电压模式神经元电路

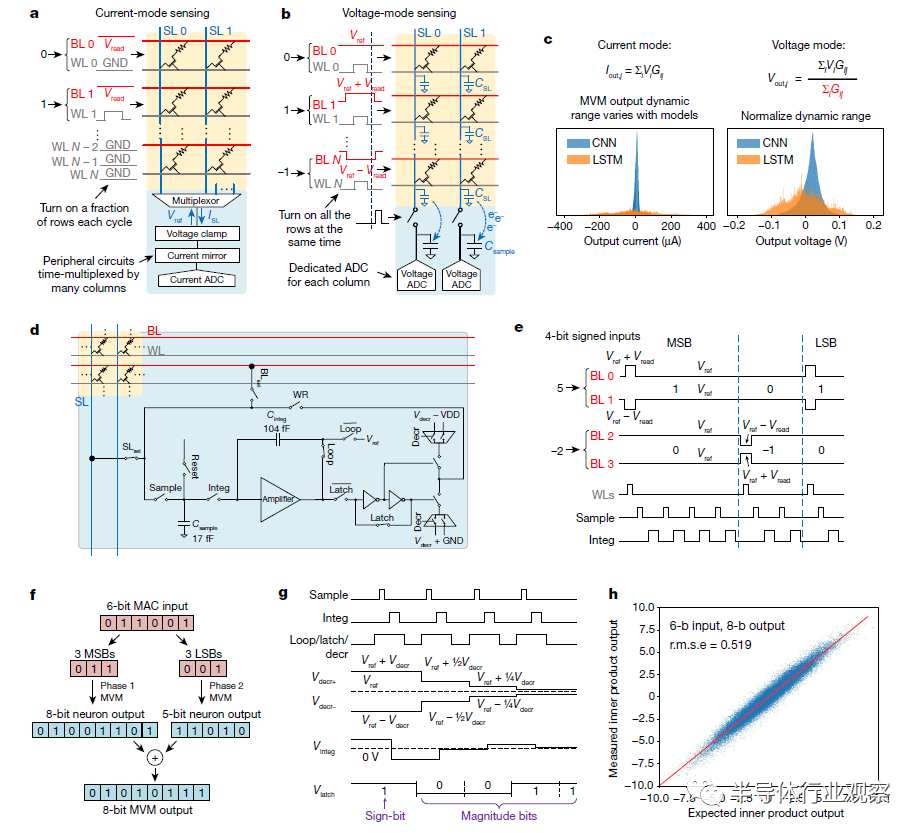

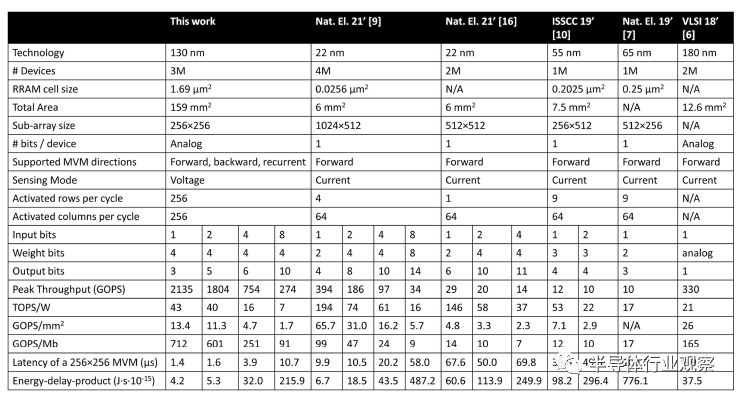

图 1d 和扩展数据表 1 显示,只管是在较旧的手艺节点上制造的,但相比于以前*进的基于 RRAM 的 CIM 芯片,NeuRRAM 芯片在种种 MVM 输入和输出位精度丈量上的 EDP 降低了 1.6 到 2.3 倍,盘算密度提高了 7 到 13 倍(以每百万 RRAM 的吞吐量权衡)。丈量讲述的能量和延迟通过执行具有 256 × 256 权重矩阵的 MVM获得的。值得注重的是,这些数字和之前 RRAM-CIM 事情中讲述的数字代表了当阵列行使率为 100% 时到达的峰值能效,而且不思量中央数据传输所破费的能量。需要全心设计片上网络和程序调剂,以实现优越的端到端应用级能效。

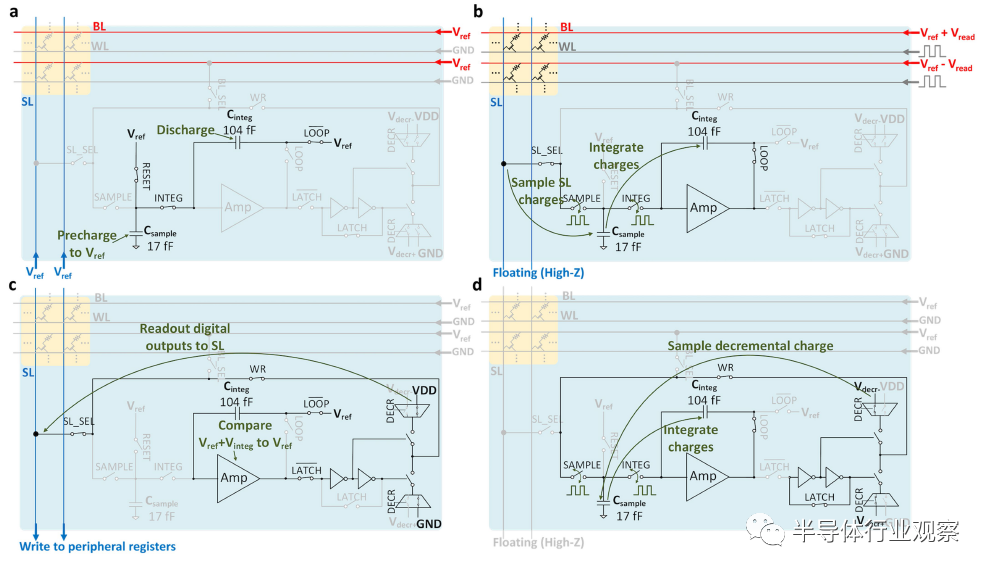

NeuRRAM的EDP 改善的要害是一种新颖的内存 MVM 输出传感方案。通例方式是使用电压作为输入,并凭证欧姆定律丈量电流作为效果(图 3a)。这种电流模式检测方案不能充实行使 CIM 的高并行性。首先,同时开启多行会导致较大的阵列电流。吸收大电流需要外围电路使用大晶体管,其面积需要通过多列之间的时分复用来分摊,这限制了“列并行” 。其次,差异神经网络层发生的 MVM 效果具有截然差其余动态局限(图 3c)。在云云宽的动态局限内优化 ADC 是很难题的。为了平衡动态局限,设计通常在每个周期激活一部门输入线以盘算部门和,因此需要多个周期来完成 MVM,这限制了“行并行性” 。

NeuRRAM 通过实现电压模式传感方案的神经元电路提高了盘算并行性和能源效率。神经元通过直接感测 BL 或 SL 线电容 (图 3b)上的稳固开路电压来执行 MVM 输出的模数转换:电压输入在 BL 上驱动,而 SL 保持浮动,反之亦然,详细取决于 MVM 偏向。激活 WL 才会启动 MVM 操作。输出线上的电压稳固为输入线上驱动的电压的加权平均值,其中权重是 RRAM 电导。在停用 WL 后,通过将输出线上的电荷转移到神经元采样电容器(图 3d 中的Csample)来对输出举行采样。然后,神经元将此电荷累积到积分电容器 ( C integ ) 上,用于随后的模数转换。

这种电压模式感测无需耗电和占用面积的外围电路用于在钳位电压的同时吸收大电流,从而提高能量和面积效率并消除输出时分复用。同时,由于电压输出中的电导加权导致的权重归一化(图 3c)可以使差异权重矩阵的自动输出动态局限归一化。因此,差异权重维度的 MVM 都可以在一个周期内完成,显着提高了盘算吞吐量。为了从最终效果中消除归一化因子,我们预先盘算其值并将其乘回ADC 的数字输出。

我们的电压模式神经元支持具有 1 位到 8 位输入和 1 位到 10 位输出的 MVM。多位输入以位串行方式实现,其中电荷被采样并集成到C integ上,延续 2 n - 1个周期,用于第n个*有用位(LSB)(图 3e)。对于大于 4 位的 MVM 输入,我们将位序列分成两段,划分盘算每个段的 MVM,并以数字方式执行移位加法以获得最终效果(图 3f)。这种两相输入方案提高了能源效率并战胜了高输入精度下的电压削顶。

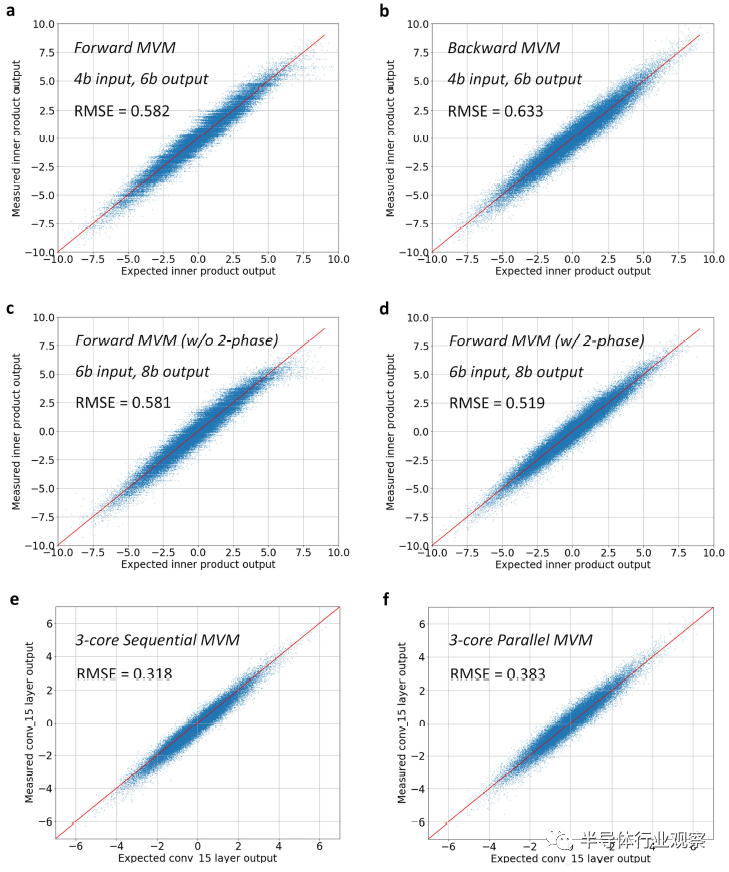

多位输出是通过二进制搜索历程天生的(图 3g)。每个周期,神经元从C integ中添加或减去Csample * Vdecr的电荷量,其中V decr是所有神经元共享的偏置电压。然后神经元将C integ上的总电荷与牢固阈值电压V ref举行对照,以天生 1 位输出。从*有用位 (MSB) 到*有用位 (LSB), V decr每个周期减半。与其他实现二进制搜索的 ADC 架构相比,我们的 ADC 方案消除了算法 ADC 的残差放大器,而且不需要像逐次迫近寄存器 (SAR) ADC 那样为每个 ADC 天生参考电压的单独 DAC 。相反,我们的 ADC 方案允许在所有神经元之间共享单个数模转换器 (DAC),以摊销 DAC 面积,从而实现更紧凑的设计。通过对照理想效果和丈量效果来验证多位 MVM,如图 3h 和扩展数据图 5 所示。有关多位输入和输出实现的更多细节可以在方式中找到。

神经元也可以重新设置以在需要时直接实现整流线性单元 (ReLU)/sigmoid/tanh 作为激活。此外,它通过将线性反馈移位寄存器 (LFSR) 模块天生的伪随机噪声注着迷经元积分器,支持随机激活函数的概率采样。所有神经元电路操作都是通过在差其余操作阶段动态地将神经元中的单个放大器设置为积分器或对照器来执行的,如方式中所述。这导致比在统一模块中合并 ADC 和神经元激活功效的其他事情更紧凑的设计。只管大多数现有的 CIM 设计使用多行多列的时间复用 ADC 来摊销 ADC 面积,但我们的神经元电路的紧凑性允许我们为每对 BL 和 SL 专用一个神经元,并将神经元与内部的 RRAM 装备慎密交织TNSA 架构,如扩展数据图 11d 所示。

图 3 |具有多位输入和输出的电压模式 MVM。

a ,传统的电流模式感测方案需要在每个周期激活总N行的一小部门,以限制总电流I SL和跨多列的时分复用 ADC 以摊销 ADC 面积,从而限制其盘算并行性。b , NeuRRAM 接纳的电压模式感应可以在单个周期内激活所有行和所有列,从而实现更高的并行度。c ,来自 CNN 层和 LSTM 层的 MVM 输出漫衍(权重归一化到相同局限)。电压模式感应本质上尺度化了输出动态局限的普遍转变。d ,电压模式神经元电路示意图,其中 BL sel 、SL sel 、Sample、Integ、Reset、Latch、Decr 和 WR 是控制开关状态的数字信号。e ,采样波形以执行 MVM 和 4 位有符号输入数模转换。WL 每幅度位脉冲一次;对第n个 LSB执行 2 n - 1次采样和积分。f 、两相MVM:对于大于4位的输入精度,输入分为MSB段和LSB段。MVM 和 ADC 对每个段划分执行,然后举行移位和加法以获得最终输出。g ,采样波形以执行 5 位带符号输出模数转换。符号位首先由对照操作天生。幅度位是通过在C integ上加/减电荷实现的二进制搜索历程天生的。从 MSB 到 LSB,加/减电荷每一位减半。h ,芯片丈量的 64 × 64 MVM 输出与 4 位输入和 6 位输出下的理想输出。

硬件算法协同优化

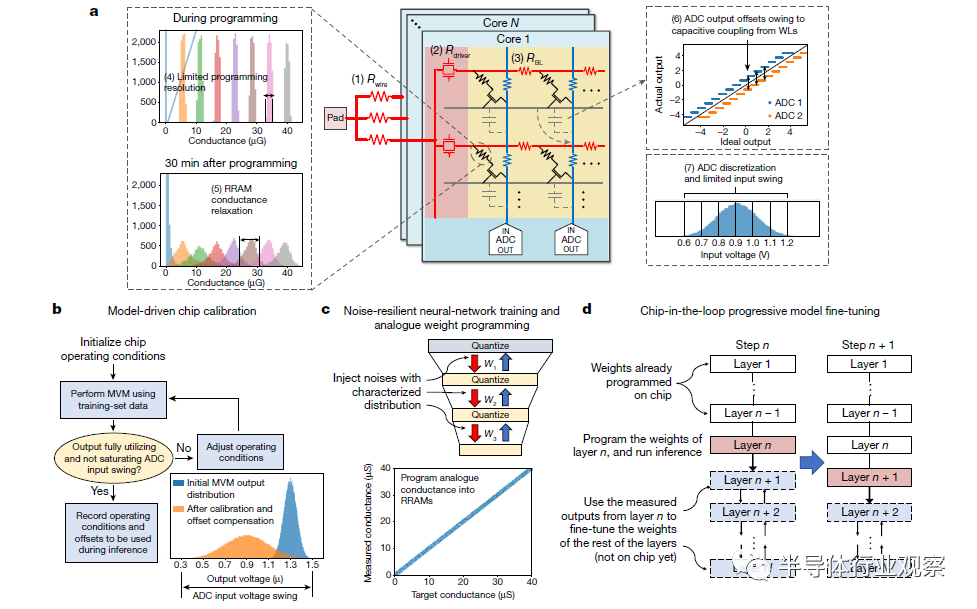

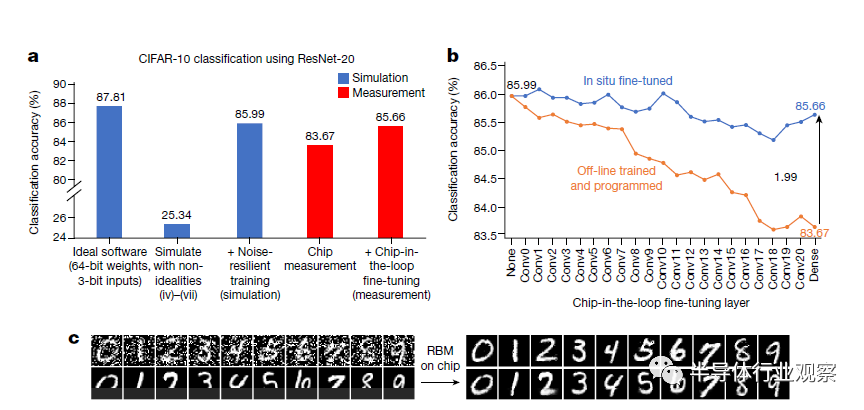

芯片架构和电路设计的创新为 NeuRRAM 带来了*的效率和可重构性。为了完成这个故事,我们必须确保在种种电路和装备的非理想情形下都能保持 AI 推理的准确性。我们开发了一套硬件算法协同优化手艺,使 NeuRRAM 能够在差其余 AI 应用程序中提供软件可比的精度。主要的是,本文中先容的所有 AI 基准测试效果完全来自对完整数据集的硬件丈量。只管大多数先前的起劲(除了少数破例)已经讲述了使用硬件表征和软件模拟夹杂的基准测试效果,例如,使用丈量的装备特征在软件中模拟阵列级 MVM 历程,这种方式通常无法对现实硬件中存在的非理想模子集举行完整地建模。如图 4a 所示,这些非理想可能包罗(1)输入线( Rwrite)上的电压降,(2)RRAM 阵列驱动器( Rdriver)上的电压降和(3)交织线(例如 BL 电阻R BL ),(4) 受限的 RRAM 编程分辨率,(5) RRAM 电导驰豫 ,(6) 来自同时切换阵列线的电容耦合,以及 (7) 受限的 ADC 分辨率和动态局限。我们的实验注释,在仿真中省略某些非理想会导致对推理准确性的过分乐观展望。例如,图 5a 中的第三和第四条显示 CIFAR-10 分类的仿真和丈量之间的准确度差异为 2.32% ,而仿真仅思量了非理想情形 (5) 和 (7),而这则是以前的研究最常举行的建模。

图 4 |提高 NeuRRAM 推理精度的硬件算法协同优化手艺。

a ,内存中MVM的种种装备和电路非理想性(符号为(1)到(7))。b ,模子驱动芯片校准手艺,用于搜索*芯片事情条件并纪录偏移以供后续消除。c ,噪声弹性神经网络训练手艺,通过噪声注入训练模子。噪声漫衍是从硬件表征中获得的。训练的权重被编程为没有量化的 RRAM 的延续模拟电导,如底部的延续对角带所示。d , Chipin-the-loop渐进微调手艺:权重一次一层地逐渐映射到芯片上。来自第n层的硬件丈量输出用作输入以微调剩余的层n 1 到N 。

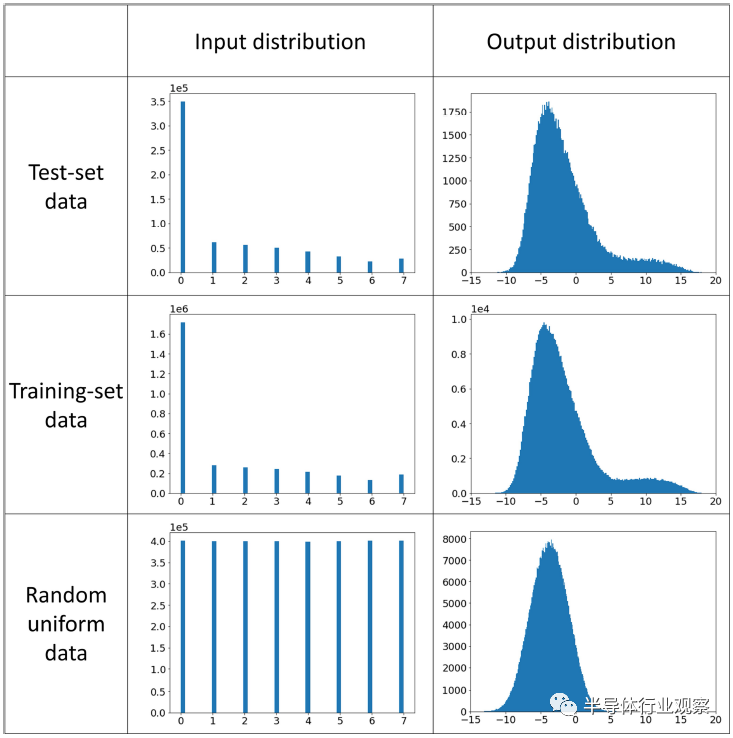

我们的硬件算法协同优化方式包罗三种主要手艺:(1)模子驱动芯片校准,(2)抗噪声神经网络训练和模拟权重编程,以及(3)芯片在环渐进模子微调。模子驱动芯片校准使用真实模子权重和输入数据来优化芯片事情条件,例如输入电压脉冲幅度,并纪录任何 ADC 偏移,以便在推理时代举行后续抵消。理想情形下,MVM 输出电压动态局限应充实行使 ADC 输入摆幅,以*限度地削减离散化误差。然而,若是没有校准,纵然电压模式传感的权重归一化效应,MVM 输出动态局限也会随着网络层的转变而转变。为了将 MVM 校准到*动态局限,对于每个网络层,我们使用训练集数据的子集作为校准输入来搜索*操作条件(图 4b)。扩展数据图 6 显示了差其余校准输入漫衍导致差其余输出漫衍。为了确保校准数据能够亲热模拟测试时看到的漫衍,因此在校准时代使用训练集数据而不是随机天生的数据至关主要。值得注重的是,当在多个内核上并行执行 MVM 时,这些共享的偏置电压不能单独针对每个内核举行优化,这可能会导致次优的事情条件和分外的精度损失(详见方式)。

图 5 |丈量效果显示了硬件算法协同优化手艺的有用性。

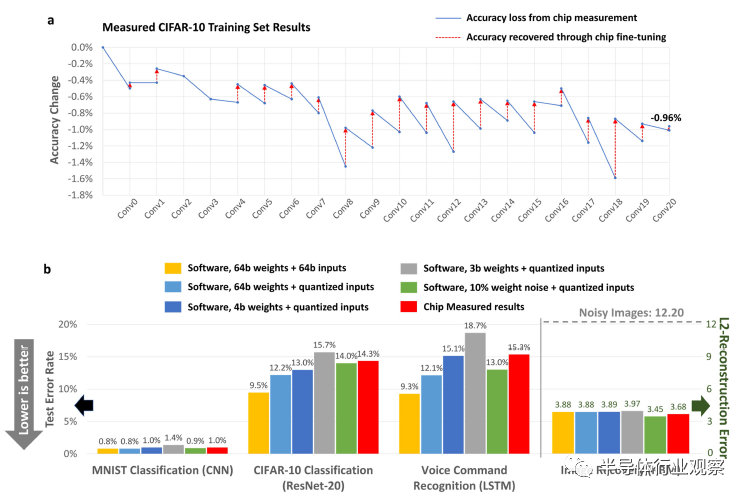

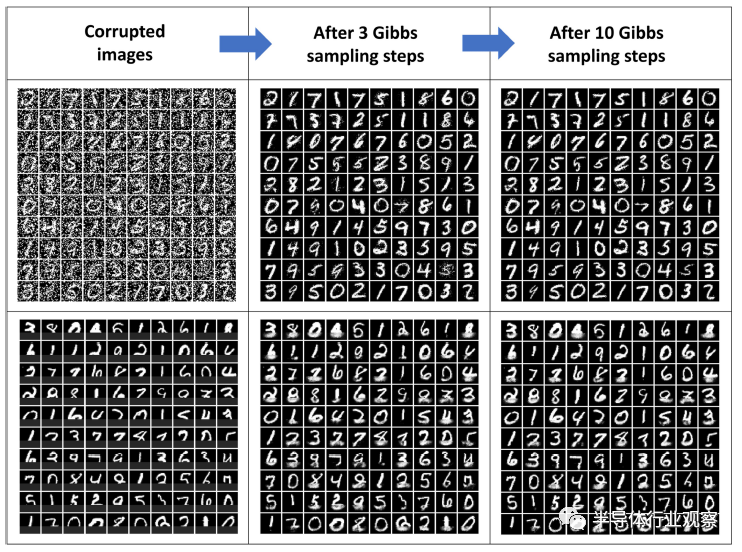

a ,仿真(蓝色)和丈量(红色)CIFAR-10 测试集分类精度。b ,CIFAR-10 在芯片在环微调的各个时间步的分类精度。从左到右,每个数据点代表一个新层(Conv0 到 Dense)编程到芯片上。通过使用该层的硬件丈量输出作为软件模拟的其余层的输入来评估该层的精度。两条曲线对照了在训练时代应用和不应用微调的测试集推理精度。c ,基于 RBM 的噪声图像恢复(顶部)和在 NeuRRAM 上丈量的部门遮挡图像(底部)的图像恢复。

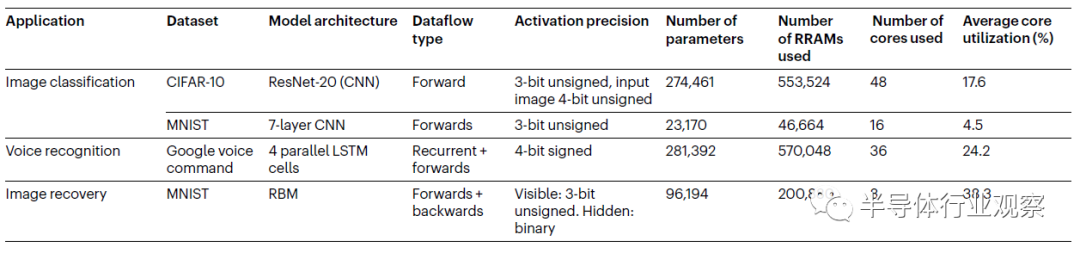

表 1 |在 NeuRRAM 上展示的 AI 应用和模子总结

RRAM 电导驰豫和读取噪声等随机非理想因素会降低盘算的信噪比 (SNR),从而导致推理精度下降。以前的一些事情通过限制每个 RRAM 单元存储单个位并使用多个单元编码更高精度的权重来获得更高的 SNR 。这种方式降低了权重存储密度。随同着上述方式,神经网络使用量化到响应精度的权重举行训练。相比之下,我们行使 RRAM 的内在模拟可编程性直接存储高精度权重并训练神经网络以容忍较低的 SNR。我们没有使用量化权重举行训练,这相当于将平均噪声注入权重,而是使用高精度权重训练模子,同时使用从 RRAM 装备丈量的漫衍注入噪声。NeuRRAM 上的 RRAM 的特点是具有高斯漫衍的电导扩展,主要由电导弛豫引起。因此,我们在训练时代将高斯噪声注入权重,类似于之前的研究。图 5a 显示该手艺显着提高了模子对噪声的免疫能力,从没有噪声注入的 CIFAR-10 分类准确度 25.34% 到有噪声注入的 85.99%。训练后,我们使用迭代写入-验证手艺将非量化权重编程为 RRAM 模拟电导,如方式中所述。该手艺使 NeuRRAM 能够实现与在种种应用程序中使用 4 位权重训练的模子相当的推理精度,同时仅使用两个 RRAM 单元对每个权重举行编码,这比以前需要每个位一个 RRAM 单元的研究密度高两倍。

通过应用上述两种手艺,我们已经可以在谷歌语音下令识别、MNIST 图像恢复和 MNIST 分类上丈量与具有 4 位权重的软件模子相当或更好的推理精度(图 1e)。对于更深条理的神经网络,我们发现那些对 MVM 输出具有非线性影响的非理想因素(例如电压降)所导致的误差可以通过层累积,而且变得加倍难以缓解。此外,多核并联MVM会导致较大的瞬时电流,进一步加剧输入线电压降等非理想情形(图4a中的(1))。效果,在深度 CNN ResNet-20上执行多核并行推理时, CIFAR-10 分类的丈量精度(83.67%)仍比 4 位权重软件模子低 3.36%( 87.03%)。

为了弥合这种精度差距,我们引入了一种芯片在环渐进式微调手艺。芯片在环训练通过直接在芯片上丈量训练误差来减轻非理想的影响。以前的事情注释,使用从硬件丈量输出盘算的反向流传梯度对最终层举行微调有助于提高准确性。我们发现这种手艺在匹敌那些非线性非理想性方面效果有限。这种手艺还需要重新编程 RRAM 装备,这会消耗分外的能量。我们的芯片在环渐进式微调通过行使深度神经网络的固有非线性通用迫近能力战胜了非线性模子误差,而且进一步消除了对权重重新编程的需要。图 4d 说明晰微调历程。我们逐步将权重一次一层地编程到芯片上。在对层举行编程后,我们使用芯片上的该层上边的训练集数据执行推理,,并使用丈量的输出来微调在软件中训练的剩余层。在下一个时间步,我们对芯片上的下一层举行编程和丈量。我们重复这个历程,直到所有层都被编程。在此历程中,编程层的非理想性可以通过训练由剩余层逐步抵偿。图 5b 显示了这种渐进式微调手艺的功效。从左到右,每个数据点代表一个新层编程到芯片上。通过使用该层的芯片丈量输出作为软件中其余层的输入来评估每一层的精度。使用这种手艺,累积的 CIFAR-10 测试集推理精度提高了 1.99%。扩展数据图 8a 进一步说明晰微调在每一层恢复训练集精度损失的水平,证实了该方式在弥合软件和硬件丈量之间的精度差距方面的有用性。

使用上述手艺,我们在所有丈量的 AI 基准义务中实现了与使用 4 位权重训练的软件模子相当的推理精度。图 1e 显示我们使用 7 层 CNN 在 MNIST 手写数字识别上实现了 0.98% 的错误率,在使用 ResNet-20 的 CIFAR-10 工具分类上实现了 14.34% 的错误率,在使用 Google 语音下令识别时用一个4 单元 LSTM实现了 15.34% 的错误率,与使用 RBM 举行 MNIST 图像恢复的原始噪声图像相比,L2 图像重修误差削减了 70%。其中一些数字尚未到达全精度数字实现所到达的精度。精度差距主要来自输入和激活的低精度( ≤ 4 位)量化,尤其是在最敏感的输入和输出层。例如,扩展数据图 8b 展示了一项消融研究,该研究注释仅将输入图像量化为 4 位会导致 CIFAR-10 分类的准确度下降 2.7%。相比之下,输入层仅占 ResNet-20 模子的 1.08% 的盘算和 0.16% 的权重。因此,它们可以以很少的开销应用到更高精度的数字盘算单元。此外,应用更先进的量化手艺和优化训练程序(如数据增强和正则化)可能会进一步提高量化软件模子和硬件丈量效果的准确性。

表 1 总结了每个展示模子的主要特征。大多数基本的神经网络层和操作都在芯片上实现,包罗所有卷积层、全毗邻层和循环层、神经元激活函数、批量归一化和随机采样历程。其他操作,例如平均池化和元素级乘法,在与 NeuRRAM 集成在统一块板上的 FPGA 上实现(扩展数据图 11a)。每个模子都是通过将权重分配给单个 NeuRRAM 芯片上的多个内核来实现的。我们开发了一个软件工具链,以便在芯片上轻松部署 AI 模子。实现细节在方式中形貌。从基本上说,每个选定的基准代表了一类通用的边缘 AI 义务:视觉识别、语音处置和图像去噪。这些效果证实了 TNSA架构的多功效性和硬件算法协同优化手艺的普遍适用性。

NeuRRAM 芯片通过在整个设计条理上举行创新,同时提高了现有 RRAM-CIM 硬件的效率、天真性和准确性,从支持可重新设置数据流偏向的 TNSA 架构到节能和面积高效的电压模式神经元电路,以及一系列算法-硬件协同优化手艺。这些手艺可以更普各处应用于其他非易失性电阻存储器手艺,例如相变存储器、磁阻RAM 和铁电场效应晶体管 。展望未来,我们预计 Neu-RRAM的峰值能效 (EDP) 将再提高两到三个数目级,同时在从 130-nm 扩展到 7-nm CMOS 和 RRAM 手艺时支持更大的 AI 模子(详见方式) .具有片上网络的多核架构设计可实现高效和多功效的数据传输和阵列间流水线,这可能是 RRAM-CIM的下一个主要挑战,需要通过进一步的跨层相助来优化。随着电阻式存储器继续向提供 TB 级片上存储器扩展,这种协同优化方式将为边缘的 CIM 硬件配备足够的性能、效率和多功效性,以执行庞大的 AI 义务,而这些义务现现在只能在云服务器上举行。

方式

内核框图和操作模式

图2d和扩展数据图1显示了单个CIM内核的框图。为了支持通用的MVM偏向,大部门设计在行(BL和WL)和列(SL)偏向上是对称的。行和列寄存器文件存储MVM的输入和输出,可以通过串行外设接口(SPI)或使用8位地址解码器的随机接见接口选择一个寄存器条目从外部写入,也可以在内部写入由神经元。SL外围电路包罗一个LFSR块,来天生用于概率采样的伪随机序列。它由两个反向流传的LFSR链实现。对两条链的寄存器举行异或运算以天生空间不相关的随机数。控制器块吸收下令并向BL/WL/SL外围逻辑和神经元天生控制波形。它包罗一个基于延迟线的脉冲发生器,脉冲宽度局限在1ns到10ns。它还实现了用于在空闲模式下关闭内核的时钟门控和电源门控逻辑。TNSA的每个WL、BL和SL都由一个驱动器驱动,该驱动器由多个提供差异电压的传输门组成。凭证存储在寄存器文件中的值和控制器发出的控制信号,WL/BL/SL逻辑决议每个传输门的状态。

该内核具有三种主要操作模式:权重编程模式、神经元测试模式和MVM模式(见扩展数据图1)。在权重编程模式下,选择单独的RRAM单元举行读写。为选择单个单元,在行和列解码器的辅助下,通过随机接见将响应行和列的寄存器编程为“1”,而其他寄存重视置为“0”。WL/BL/SL逻辑打开响应的驱动器传输门以在选定内核上举行设置/复位/读取电压。在神经元测试模式下,WL保持在接地(GND)。神经元通过它们的BL或SL开关直接从BL或SL驱动器吸收输入,绕过RRAM装备,这使我们能够自力于RRAM阵列来表征神经元。在MVM模式下,每个输入BL和SL被驱动到Vref-Vread、Vref Vread或Vref,详细取决于该行或列的寄存器值。若是MVM在BL-to-SL偏向,我们激活输入向量长度内的WL,而其余的保持在GND;若是MVM在SL-to-BL偏向,我们激活所有WL。在神经元完成模数转换后,从BL和SL到寄存器的通道门将被打开,并允许读取神经元状态。

装备制造

NeuRRAM中的RRAM阵列接纳单晶体管单电阻(1T1R)设置,其中每个RRAM器件堆叠在选择器NMOS晶体管的顶部并与选择器NMOS晶体管串联毗邻,该晶体管切断潜行路径并在RRAM编程和读取时代限制电流巨细。选择器NMOS、CMOS外围电路和底部的四个后端互连金属层接纳尺度的130纳米工艺制造。由于RRAM形成和编程需要更高电压,选择器NMOS和直接与RRAM阵列接口的外围电路使用额定电压为5V的厚氧化层输入/输出(I/O)晶体管。神经元、数字逻辑、寄存器等当中的所有其他CMOS电路都使用额定电压为1.8V的焦点晶体管。

如图2c所示,RRAM器件夹在金属4层和金属5层之间。在代工厂完成CMOS和底部四层金属层的制造后,我们使用实验室工艺完成RRAM器件和金属5互连以及顶部金属焊盘和钝化层的制造。RRAM器件堆叠由氮化钛(TiN)底部电极层、氧化铪(HfOx)开关层、氧化钽(TaOx)热增强层和TiN顶部电极层组成。

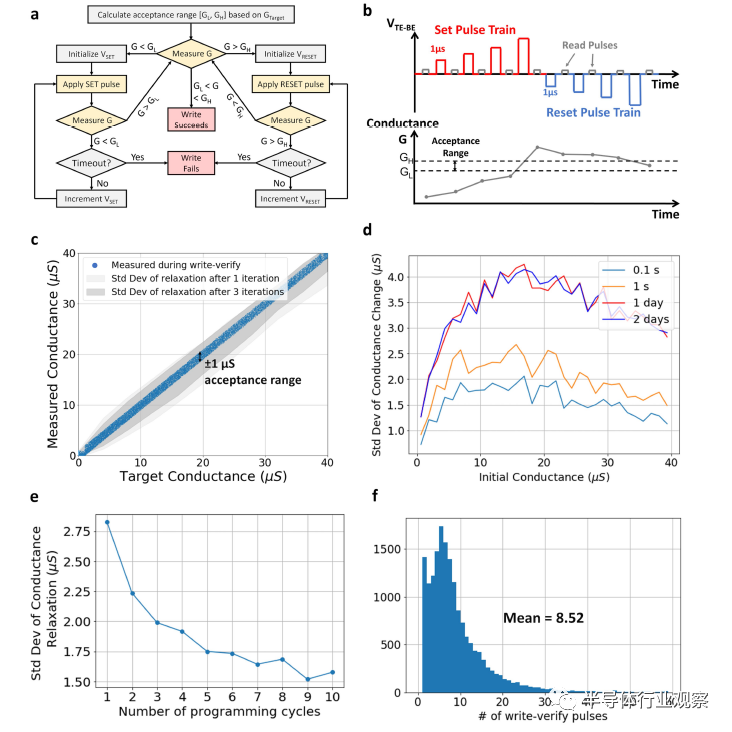

RRAM写入-验证编程和电导弛豫

每个神经网络权重由沿统一列的相邻行上的两个RRAM单元之间的差分电导编码。*个RRAM单元编码正权重,若是权重为负,则被设置为低电导状态(gmin);*个单元编码负权重,若是权重为正,则将其编程为gmin。在数学上,两个单元的电导划分为

和

其中gmax和gmin是RRAM的*和最小电导,wmax是权重的**值,W是未量化的高精度权重。

我们使用增量脉冲写入验证手艺将RRAM单元编程为其目的电导。扩展数据图3a、b注释了该历程。我们首先丈量电池的初始电导,若是该值低于目的电导,我们应用弱设置脉冲来略微增添单元电导。然后我们再次读取单元,若是该值仍低于目的值,我们将应用另一个设置脉冲来少量增添其幅度。我们重复上述操作,直到单元电导在目的值的可接受局限内或跨越目的。在后一种情形下,我们将脉冲极性反转为复位,并重复与设置相同的历程。在设置/重置脉冲序列时代,电池电导可能会上下反弹多次,直到最终进入可接受局限或到达超时限制。

在选择编程条件时有一些权衡。(1)较小的接受局限和较高的超时限制提高了编程精度,但需要较长的时间。(2)较高的gmax可提高推理历程中的SNR,但会导致更高的能耗和更多无法到达高电导的单元的编程失败。在我们的实验中,我们将初始设置脉冲电压设置为1.2V,将复位脉冲电压设置为1.5V,两者的增量均为0.1V,脉冲宽度为1μs。读取RRAM需要1-10μs,详细取决于其电导率。接受局限为目的电导的±1μS。超时限制为30次设置-复位极性反转。我们对所有模子使用gmin=1μS,对CNNs使用gmax=40μS,对LSTM和RBMs使用gmax=30μS。通过这样的设置,可以将99%的RRAM单元编程到超时限制内的可接受局限。平均每个单元需要8.52个设置/重置脉冲。在当前的实现中,这种写验证历程的速率受到DAC和ADC的外部控制的限制。若是将所有内容集成到单个芯片中,这样的写入验证将平均每个单元需要56微秒。使用多个DAC和ADC以在多个单元上并行执行写入验证将进一步提高RRAM编程吞吐量,但价值是更大的芯片面积。

除了较长的编程时间之外,不使用过小的写入验证接受局限的另一个缘故原由是RRAM电导弛豫。RRAM电导在编程后随时间转变,大部门转变发生在编程后的短时间内(小于1秒)内,如扩展数据图3d所示。在文献中,突然的初始转变被称为“电导弛豫”。它的统计量在所有电导状态下都遵照高斯漫衍,除非电导靠近gmin。扩展数据图3c、d显示了在整个gmin到gmax电导局限内丈量的电导弛豫。我们发现,由于电导弛豫导致的编程精度损失远高于由写入验证接受局限引起的损失。所有初始电导水平的平均尺度误差约为2.8μS。*尺度误差约为4μS,靠近gmax的10%。

为了减轻电导弛豫,我们使用迭代编程手艺。我们多次迭代RRAM阵列,在每次迭代中,我们丈量所有的细胞并重新编程那些电导偏离可接受局限的单元。扩展数据图3e显示随着更多的编程迭代,尺度误差变得更小。经由3次迭代,尺度差变为2μS左右,与初始值相比下降了29%。我们在所有神经网络演示中使用3次迭代,并在编程后至少30分钟执行推理,这样测得的推理精度就可以注释这种电导弛豫效应。通过将迭代编程与我们的硬件感知模子训练方式相连系,可以大大减轻弛豫的影响。

具有多位输入和输出的MVM的实现

神经元和外围电路以可设置的输入和输出位精度支持MVM。MVM操作由初始化阶段、输入阶段和输出阶段组成。扩展数据图4说明晰神经元电路的操作。在初始化阶段(扩展数据图4a),所有BL和SL都被预充电到Vref。神经元的采样电容器Csample也被预充电到Vref,而积分电容器Cinteg被放电。

如图3b所示在输入阶段,每条输入线(BL或SL,取决于MVM偏向)通过三个传输门被驱动到三个电平之一,Vref-Vread、Vref和Vref Vread。在前向MVM时代,在差分行权重映射下,每个输入都应用于一对相邻的BL。两个BL被驱动到相对于Vref的相反电压。即当输入为0时,两根线都被驱动到Vref;当输入为 1时,两条线被驱动到Vref Vread和Vref-Vread;当输入为-1时,为Vref-Vread和Vref Vread。在反向MVM时代,每个输入都应用于单个SL。在神经元完成模数转换后,以数字方式执行差分运算。

在对输入线举行偏置之后,我们对具有输入的WL举行10ns的脉冲处置,同时保持输出线悬空。随着输出线的电压稳固到

,其中Gij示意RRAM在第i行和第j列的电导,我们关闭WL。然后,我们将输出线寄生电容上剩余的电荷采样到位于神经元内的Csample,然后将电荷积分到Cinteg上,如扩展数据图4b所示。采样脉冲为10ns(受FPGA的100MHz外部时钟限制);积分脉冲为240ns,受大积分电容器(104fF)的限制,为了确保功效准确性和测试差其余神经元事情条件而守旧地选择了该电容器。

多位输入数模转换以位串行方式执行。对于第n个LSB,我们向输入线施加单个脉冲,然后对来自输出线的电荷举行采样并将其积分到Cinteg上2n-1个周期。在多位输入阶段竣事时,完整的模拟MVM输出作为电荷存储在Cinteg上。例如,如图3e所示,当输入向量是具有1个符号位和3个幅度位的4位有符号整数时,我们首先将对应于*个(*有用)幅度位的脉冲发送到输入线,然后采样和积分一个周期。对于*和第三幅度位,我们再次对每个位的输入线施加一个脉冲,然后划分对两个周期和四个周期举行采样和积分。一样平常来说,对于n位有符号整数输入,我们总共需要n-1个输入脉冲和2n-1-1个采样和积分周期。

由于采样和积分周期呈指数增进,这种多位输入方案对于高输入位精度变得低效。此外,由于在Cinteg集成的电荷随着更多的集成周期而饱和,净空限幅成为一个问题。可以通过使用较低的Vread来战胜余量削波,但会以较低的SNR为价值,因此在使用更高精度的输入时,整体MVM精度可能不会提高。例如,扩展数据图5a、c显示了MVM效果的丈量均方根误差(r.m.s.e.)。由于SNR较低,与4位(r.m.s.e.=0.582)相比,将输入量化为6位(r.m.s.e.=0.581)不会提高MVM精度。

为领会决这两个问题,我们对大于4位的输入使用双相输入方案,图3f展示了该历程。为了执行具有6位输入和8位输出的MVM,我们将输入分为两个部门,*个包罗三个MSB,*个包罗三个LSB。然后我们执行MVM,包罗划分为每个段的输出模数转换。对于MSB,神经元(ADC)设置为输出8位;对于LSB,神经元输出5位。最终效果是通过在数字域中对两个输出举行移位和相加获得的。扩展数据图5d显示该方案降低了MVM的r.m.s.e。从0.581到0.519。扩展数据图12c-e进一步注释,这种两相方案既扩展了输入位精度局限,又提高了能量效率。

最后,在输出阶段,模数转换再次通过二进制搜索历程以位串行方式执行。首先,为了天生输出的符号位,我们断开放大器的反馈回路,将积分器酿成对照器(扩展数据图4c)。我们将Cinteg的右侧驱动到Vref。若是积分电荷为正,则对照器输出为GND,否则为电源电压VDD。然后对照器输出被反转、锁存并通过神经元BL或SL开关读出到BL或SL,然后再写入外围BL或SL寄存器。

为了天生k个幅度位,我们从Cinteg中添加或减去电荷(扩展数据图4d),然后举行k周期的对照和读出。从MSB到LSB,每个周期增添或削减的电荷量减半。加法照样减法由上一个周期的锁存器中存储的对照效果自动确定,图3g展示了这样一个历程。在*个周期中首先天生并锁存符号位“1”,示意正输出。为了发生*有用幅度位,锁存器打开从Vdecr-=Vref-Vdecr到Csample的路径。然后通过打开放大器的负反馈回路将Csample采样的电荷积分到Cinteg上,从而从Cinteg中减去CsampleVdecr的电荷量。在本例中,CsampleVdecr大于Cinteg上的原始电荷量,因此总电荷变为负数,对照器天生“0”输出。为了发生*个幅度位,Vdecr减半。这一次,锁存器打开从Vdecr =Vref 1/2Vdecr到Csample的路径。由于积分后Cinteg上的总电荷仍然为负,因此对照器在此周期内再次输出“0”。我们重复这个历程,直到发生*有用幅度位。请注重,若是初始符号位为“0”,则所有后续幅度位都市在读出之前反转。

这种输出转换方案类似于算法ADC或SARADC,对于n位输出执行n个周期的二进制搜索。差异之处在于算法ADC使用残差放大器,而SARADC需要为每个ADC配备一个多位DAC,而我们的方案不需要残差放大器,而且使用输出2×(n−1)的单个DAC差其余Vdecr 和Vdecr-电平,由所有神经元(ADC)共享。因此,我们的方案通过对用于集成和对照的放大器举行时间多路复用、消除残差放大器以及在CIM内核中的所有神经元之间摊销DAC区域来实现更紧凑的设计。对于使用麋集存储器阵列的CIM设计,这种紧凑的设计允许每个ADC通过较少数目的行和列举行时分复用,从而提高吞吐量。

总而言之,可设置的MVM输入和输出位精度以及种种神经元激活函数都是使用四种基本操作的差异组合实现的:采样、积分、对照和电荷递减。主要的是,所有四种操作均由设置为差异反馈模式的单个放大器实现。因此,该设计同时实现了多功效性和紧凑性。

多内核并行MVM

NeuRRAM支持在多个CIM内核上并行执行MVM。多核MVM给盘算准确性带来了分外的挑战,由于在单核MVM中没有体现的某些硬件非理想性随着内核的增多而变得加倍严重。它们包罗输入线上的电压降、内核间转变和电源电压不稳固性。输入线上的压降(图4a中的非理想性(1))是由多个内核同时从共享电压源吸收的大电流引起的。它使存储在每个焦点中的等效权重随应用的输入而转变,因此对MVM输出具有非线性的输入相关影响。此外,由于差其余焦点与共享电压源的距离差异,它们会履历差其余电压降。因此,我们不能为每个内核单独优化读取电压幅度,以使其MVM输出准确地占有整个神经元输入动态局限。

这些非理想因素配合降低了多核MVM的准确性。扩展数据图5e、f显示,当在3个核上并行执行卷积时,相比于通过在3个内核上顺序执行卷积获得的r.m.s.e.=0.318,卷积层15的输出被丈量为具有更高的r.m.s.e(0.383)。在我们的ResNet-20实验中,我们对块1内的卷积执行双核并行MVM(扩展数据图9a),对块2和3内的卷积执行3核并行MVM。

通过使承载大瞬时电流的导线尽可能低电阻,以及接纳具有更优化拓扑的电力传输网络,可以部门缓解电压降问题。但随着使用更多内核,问题将延续存在并变得更糟。因此,我们的实验旨在研究算法-硬件协同优化手艺在缓解该问题方面的功效。此外,值得注重的是,对于全芯片实现,需要集成分外的模块,例如中央效果缓冲区、部门和累加器和片上网络,以治理内核间数据传输。还应仔细优化程序调剂,以最小化缓冲区巨细和中央数据移动所消耗的能量。只管有关于这种全芯片架构和调剂的研究,但它们超出了本研究的局限。

抗噪神经网络训练

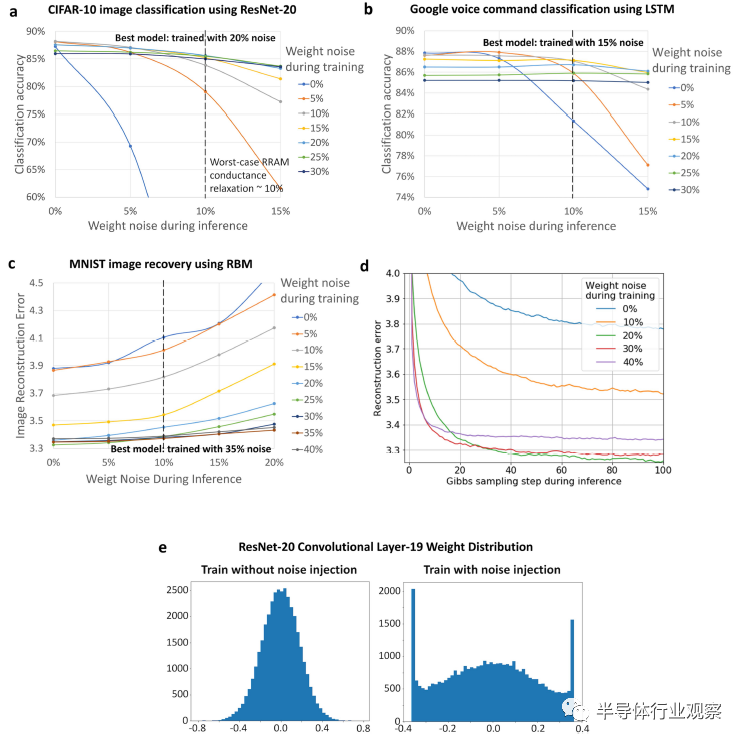

在抗噪神经网络训练时代,我们在神经网络训练的前向通报历程中将噪声注入所有全毗邻层和卷积层的权重中,以模拟RRAM电导弛豫和读取时噪声的影响。注入噪声的漫衍是通过RRAM表征获得的。我们使用迭代写入验证手艺将RRAM单元编程为差其余初始电导状态,并在30分钟后丈量它们的电导弛豫。扩展数据图3d显示丈量的电导弛豫在所有电导状态下的*值均值<1μS(gmin)。*尺度差为3.87μS,约为gmax40μS的10%,在约12μS初始电导状态下发现。因此,为了在推理历程中模拟这种电导弛豫行为,我们注入了一个均值为零且尺度误差即是层*权重10%的高斯噪声。

我们训练具有从0%到40%的差异噪声注入水平的模子,并选择在10%噪声水平下实现*推理精度的模子举行片上部署。我们发现在训练时代注入比测试更高的噪声可以提高模子的抗噪性。扩展数据图7a-c显示,在存在10%权重噪声的情形下,在CIFAR-10图像分类的20%训练时间噪声注入、15%用于Google语音下令分类和35%用于基于RBM的图像重修的情形下,获得了*测试时间准确度。

对于CIFAR-10,使用5%噪声训练的模子获得更好的初始准确率,这很可能是由于噪声注入的正则化效应。在神经网络量化文献中提到了类似的征象,其中经由量化训练的模子有时会优于全精度模子。在我们的实验中,我们没有在噪声注入之上对无噪声训练的模子应用分外的正则化,这可能导致次优精度。

对于RBM,扩展数据图7d进一步显示了重修误差若何随着使用差异噪声训练的模子的Gibbs采样步骤数而削减。一样平常来说,用较高噪声训练的模子在推理历程中收敛得更快。使用20%噪声训练的模子在100个Gibbs采样步骤竣事时到达*误差。

扩展数据图7e显示了噪声注入对权重漫衍的影响。在没有噪声注入的情形下,权重具有高斯漫衍。神经网络输出严重依赖于小部门大权重,因此容易受到噪声注入的影响。通过噪声注入,权重漫衍更平均,使模子更具抗噪性。

为了在NeuRRAM上有用地实现模子,所有卷积层和全毗邻层的输入都被量化为4位或更低。表1总结了所有模子的输入位精度。我们使用参数化裁剪激活手艺举行量化训练。我们的一些量化模子的准确性低于*进的量化模子,由于我们将<4位量化应用于神经网络最敏感的输入和输出层,研究注释这会导致精度下降很大,因此通常被清扫在低精器量化之外。为了获得更好的量化模子精度,可以对敏感的输入和输出层应用更先进的量化手艺来到达更高的精度,并在训练时代使用更优化的数据预处置、数据增强和正则化手艺。然而,这项事情的重点是在硬件和软件上实现相当的推理精度,同时保持所有这些变量相同,而不是在所有义务上获得*进的推理精度。上述量化和训练手艺对我们的软件基线和硬件丈量同样有益。

芯片在环渐进式微调

在渐进式芯片在环微调时代,我们使用来自一层的芯片丈量的中央输出来微调其余层的权重。主要的是,为了公正地评估该手艺的有用性,我们在整个微调历程中不使用测试集数据。为了制止过拟合一小部门数据,应该对整个训练集数据举行丈量。我们将学习率降低到用于训练基线模子的初始学习率的1/100,并微调了30个epoch,只管我们考察到准确度通常在前10个epoch内保持稳固。在微调时代应用相同的权重噪声注入和输入量化。

CNN、LSTM和RBM的实现

我们将CNN模子用于CIFAR-10和MNIST图像分类义务。CIFAR-10数据集由50,000张训练图像和10,000张测试图像组成,属于10个工具种别。我们使用ResNet-20执行图像分类,它包罗21个卷积层和1个全毗邻层(扩展数据图9a),层间有归一化和ReLU激活,该模子使用Keras框架举行训练。我们将所有卷积层和全毗邻层的输入量化为3位无符号定点名堂,除了*个卷积层,我们将输入图像量化为4位,由于推理精度对输入量化更敏感。对于MNIST手写数字分类,我们使用由六个卷积层和一个全毗邻层组成的七层CNN,并在层间使用*池化来对特征图巨细举行下采样。所有层的输入,包罗输入图像,都被量化为3位无符号定点名堂。

CNN的所有参数都在单个NeuRRAM芯片上实现,包罗卷积层、全毗邻层和批量归一化的参数。平均池化等其他操作在与NeuRRAM集成在统一块板上的FPGA上实现。这些操作只占总盘算量的一小部门,将它们的实现集成到数字CMOS中只会发生可忽略的开销;选择FPGA实现是为了在测试和开发历程中提供更大的天真性。

扩展数据图9a-c说明晰在芯片上映射卷积层的历程。为了在二维RRAM阵列上实现维度为H(高度)、W(宽度)、I(输入通道数)、O(输出通道数)的四维卷积层的权重,我们将前三个扁平化维度转换为一维向量,并将每个输出通道的偏置项附加到每个向量。若是误差值的局限是权重局限的B倍,我们将误差值均分并使用B行实现。此外,我们在训练后将归一化参数合并为卷积权重和误差(扩展数据图9b),并将合并的Wʹ和bʹ编程到RRAM阵列上,这样在推理时代不需要执行显式的批归一化。

在差分行权重映射方案下,卷积层的参数被转换为巨细为(2(HWI B),O)的电导矩阵。若是电导矩阵适合单个内核,则将输入向量应用于2(HWI B)行并在单个周期内扩展到O列。HWIO乘法累加(MAC)操作是并行执行的。大多数ResNet-20卷积层的电导矩阵高度为2(HWI B),大于256的RRAM阵列长度。因此,我们将它们垂直拆分为多个段,并将这些段并行映射到接见的差异内核上,或按顺序接见的内核的差异列上。权重映射计谋的细节将在下一节中形貌。

Google语音下令数据集包罗65,000个1秒长的语音下令录音,例如“是”、“向上”、“开”、“住手”等,由数千名差其余人说出。这些下令分为12类。扩展数据图9d说明晰模子架构。我们使用Mel频率倒谱系数编码方式将每40毫秒的音频片断编码为长度为40的向量。跳跃长度为20毫秒,对于每个1秒的纪录,我们有一个50步的时间序列。

我们构建了一个包罗四个并行LSTM单元的模子。每个单元格都有一个长度为112的隐藏状态。最终分类基于四个单元格的输出总和。与单个单元模子相比,4单元模子通过行使NeuRRAM芯片上的分外内核,将(未量化模子的)分类误差从10.13%降低到9.28%。在一个单元内,在每个时间步长中,我们凭证当前步的输入和上一步的隐藏状态盘算四个LSTM门(输入、激活、遗忘和输出)的值。然后我们在四个门之间执行元素操作来盘算新的隐藏状态值。最终的logit输出是凭证最后一个时间步的隐藏状态盘算的。

每个LSTM单元都有3个在芯片上实现的权重矩阵:一个巨细为40×448的输入到隐藏状态矩阵,一个巨细为112×448的隐藏状态到隐藏状态矩阵和一个隐藏状态到逻辑矩阵巨细为112×12,在FPGA上逐元素操作实现。该模子使用PyTorch框架举行训练。所有MVM的输入都被量化为4位有符号定点名堂。所有剩余的操作都被量化为8位。

RBM是一种天生概率图形模子。它不是被训练来执行诸如分类之类的判别义务,而是学习数据自己的统计结构。扩展数据图9e显示了我们的图像恢复RBM的架构。该模子由794个完全毗邻的可见神经元组成,对应于784个图像像素加上10个one-hot编码类标签和120个隐藏神经元。我们使用软件中的对比发散学习程序来训练RBM。

在推理历程中,我们将像素部门损坏或壅闭的3位图像发送到在NeuRRAM芯片上运行的模子。然后,该模子在可见和隐藏神经元之间执行十个周期。在每个循环中,神经元凭证概率漫衍从MVM输出中采样二进制状态h和v:p(hj=1_v)=σ(bj Σiviwij)和p(hj=1_v)=σ(bj Σiviwij),其中σ是sigmoid函数,ai是隐藏神经元(h)的误差,bj是可见神经元(v)的误差。采样后,我们将未损坏的像素(可见神经元)重置为原始像素值。通过盘算原始图像和恢复图像之间的平均L2重修误差来评估最终的推理性能。扩展数据图10显示了丈量的图像恢复的一些示例。

在将794×120的权重矩阵映射到芯片的多个内核时,我们只管使每个内核的MVM输出动态局限相对一致,这样恢复性能不会过分依赖任何单个内核的盘算精度。为了实现这一点,我们将相邻像素(可见神经元)分配给差其余内核,这样每个焦点都可以看到整个图像的下采样版本,如扩展数据图9f所示。行使TNSA的双向MVM功效,在每个焦点中从SL到BL偏向执行可见到隐藏神经元MVM;从BL-to-SL偏向执行hidden-to-visible神经元MVM。

多CIM内核的权重映射计谋

为了在NeuRRAM芯片上实现AI模子,我们将每个模子层的权重、误差和其他相关参数(例如,批量归一化)转换为单个二维电导矩阵,如上一节所述。若是矩阵的高度或宽度跨越单个CIM内核的RRAM阵列巨细(256×256),我们将矩阵拆分为多个较小的电导矩阵,每个矩阵的*高度和宽度为256。

在将这些电导矩阵映射到48个内核时,我们思量了三个因素:资源行使率、盘算负载平衡和电压降。主要义务是确保模子的所有电导矩阵都映射到单个芯片上,这样在推理历程中就不需要重新编程。若是电导矩阵的总数不跨越48个,我们可以将每个矩阵映射到单个内核(图2a中的情形(1))或多个内核上。当我们将单个矩阵映射到多个内核时,有两种情形。(1)当模子具有差其余盘算强度时,界说为每个权重的盘算量,对于差其余层,(例如,由于特征图尺寸较大,CNN通常对较早的层具有更高的盘算强度),我们复制盘算麋集度更高的矩阵到多个内核并并行操作它们以增添吞吐量并平衡各层的盘算负载(图2a中的情形(2))。(2)一些模子具有“宽”电导矩阵(输出维度>128),例如我们的图像恢复RBM。若是将整个矩阵映射到单个内核上,则每个输入驱动器都需要为其毗邻的RRAM提供大电流,从而导致驱动器上泛起显著的压降,从而降低推理精度。因此,当有备用内核时,我们可以将矩阵垂直拆分为多个段,并将它们映射到差其余内核上以减轻电压降(图2a中的情形(6))。

相比之下,若是一个模子有跨越48个电导矩阵,我们需要合并一些矩阵,以便它们可以适合单个芯片。较小的矩阵对角线合并,以便可以并行接见它们(图2a中的情形(3))。较大的矩阵水平合并,并通过时间复用输入行接见(图2a中的情形(4))。在选摘要合并的矩阵时,我们希望制止属于上一段中形貌的相同两个种其余矩阵:(1)盘算强度高的矩阵(例如,ResNet-20的早期层),以只管削减对吞吐量;(2)具有“宽”输出维度的那些(例如,ResNet-20的后期层具有大量输出通道)以制止较大的电压降。例如,在我们的ResNet-20实现中,总共有61个电导矩阵(扩展数据图9a:1个来自输入层,12个来自块1,17个来自块2,28个来自块3,2个来自shortcut层和1个从最后的麋集层),我们将块1和3中的每个电导矩阵映射到单个内核上,并合并剩余的矩阵以占有剩余的8个内核。

表1总结了所有模子的内核使用情形。值得注重的是,对于部门占用的内核,未使用的RRAM单元要么未成型,要么被编程为高电阻状态;推理时代不激活未使用行的WL。因此,它们在推理历程中不会消耗分外的能量。

测试系统实行

扩展数据图11a显示了NeuRRAM芯片的硬件测试系统。NeuRRAM芯片由位于OpalKelly集成FPGA板上的XilinxSpartan-6FPGA设置、吸收输入并将输出发送至XilinxSpartan-6FPGA。FPGA通过USB3.0模块与PC通讯。测试板还包罗电压DAC,可提供RRAM编程和MVM所需的种种偏置电压,以及ADC,用于在写入验证编程时代丈量RRAM电导。整个电路板的电源由尺度的“大炮式”直流电源提供。OpalKelly板上的电源毗邻器和集成开关稳压器,因此芯片操作不需要外部实验室装备。

为了能够在NeuRRAM芯片上快速实现种种机械学习应用程序,我们开发了一个软件工具链,可在各个层级提供基于Python的应用程序编程接口(API)。低级API提供对每个芯片模块的基本操作的接见,例如RRAM读写和神经元模数转换;中级API包罗实现神经网络层所需的基本操作,例如具有可设置位精度和RRAM写入验证编程的多核并行MVM;*API集成了种种中级模块,以提供神经网络层的完整实现,例如卷积层和全毗邻层的权重映射和批量推理。该软件工具链旨在让不熟悉NeuRRAM芯片设计的软件开发职员能够在NeuRRAM芯片上部署他们的机械学习模子。

功率和吞吐量丈量

为了表征差异输入和输出位精度下的MVM能效,我们划分丈量了MVM输入和输出级的功耗和延迟。总能耗和总时间是输入和输出阶段的总和,由于这两个阶段是自力执行的,以是我们可以很容易地获得输入和输出位精度的任何组合的能效。

为了丈量输入级的能量效率,我们天生一个256×256的高斯漫衍随机权重矩阵,将其分成2个段,每个段的维度为128×256,并使用差分行权重映射将这两个段编程到两个内核,我们丈量了执行1000万个MVM或相当于6550亿个MAC操作的功耗和延迟。与图1d所示的先前事情的对照使用与基准测试相同的事情负载。

扩展数据图12a显示了在差异位精度下MVM的输入和输出阶段每个操作消耗的能量。输入接纳有符号整数名堂,其中*位示意符号,其他位示意幅度。一位(二进制)和两位(三进制)显示相似的能量,由于每条输入线都被驱动到三个电压电平之一。因此,二进制输入只是三进制输入的一种特殊情形。注重,扩展数据图12a中所示的曲线是在没有两相操作的情形下获得的。效果,随着输入位精度的增添,我们能看到能量的超线性增添。与输入类似,输出也以有符号整数名堂示意。输出级能耗随输出位精度线性增进,由于每增添一位就需要一个分外的二进制搜索周期。输出级比输入级消耗更少的能量,由于它不涉及切换以更高电压驱动的高容性WL,如下所述。

对于扩展数据图12b-e中所示的MVM丈量,假设MVM输出级使用比输入高2位的精度来说明部门和累加所需的分外位精度。NeuRRAM实现的电压模式感应所需的部门和位精度远低于传统电流模式感应所需的位精度。如前所述,传统的电流感应设计每个周期只能激活一小部门行,因此需要许多部门和累加步骤来完成MVM。相比之下,所提出的电压检测方案可以在一个周期内激活所有256条输入线,因此需要较少的部门和累加步骤和较低的部门和精度。

扩展数据图12b显示了能耗细分。大部门能量用于打开和关闭毗邻到RRAM器件选择晶体管栅极的WL。这些晶体管使用厚氧化物I/O晶体管来蒙受RRAM形成和编程时代的高压。它们的尺寸足够大(宽度为1μm,长度为500nm),可为RRAM编程提供足够的电流。因此,它们需要高事情电压并为WL增添大电容,这都市导致高功耗(P=fCV2,其中f是电容充电和放电的频率)。仿真注释,256个存取晶体管中的每一个对WL孝顺约莫1.5fF;WL驱动器合计为每个WL孝顺约48fF;分外的WL电容主要来自相邻BL和WL的线间电容。若是RRAM可以通过较低的电压写入并具有较低的电导状态,而且若是可以使用具有更好驱动能力的更小晶体管,则WL能量预计会显着降低。

对于需要概率采样的应用,两个反向流传的LFSR链会天生随机伯努利噪声并将噪声作为电压脉冲注着迷经元。我们丈量每个噪声注入步骤平均消耗每个神经元121fJ,与扩展数据图12b中显示的其他能源消耗相比,这是很小的。

扩展数据图12c-e显示了执行256×256MVM时测得的延迟、峰值吞吐量和吞吐量功率效率。值得注重的是,我们使用EDP作为对照设计的品质因数,而不是吞吐量功率效率作为每秒每瓦的兆兆次操作(TOPSW-1,每次操作能量的倒数)。与该领域以前的事情类似,研究中的吞吐量和能源效率代表了CIM阵列行使率为100%时的峰值,不包罗缓冲和移动中央数据所破费的时间和能量。在单个完整的CIM芯片中集成中央数据缓冲区、部门和累加器等的未来事情应该显示在端到端AI应用程序上丈量的能效。

NeuRRAM能源效率与手艺扩展的展望

当前的NeuRRAM芯片是使用130-nmCMOS手艺制造的。我们预计能源效率会随着手艺规模的扩大而提高。主要的是,CMOS晶体管和互连的隔离缩放不足以提高整体能效。RRAM器件特征必须与CMOS配合优化。1T1R设置下的RRAM阵列密度不受制造工艺的限制,而是受RRAM写入电流和电压的限制。当前的NeuRRAM芯片使用大型厚氧化物I/O晶体管作为“T”,以蒙受>4-VRRAM形成电压并提供足够的写入电流。只有降低形成电压和写入电流,才气获得更高的密度,从而降低寄生电容,提高能效。

假设在较新的工艺节点上的RRAM器件可以在逻辑兼容的电压电平下举行编程,而且可以削减所需的写入电流以使毗邻晶体管的尺寸不停缩小,EDP的改善未来自(1)更低的操作电压(2)更小的导线和晶体管电容,即能量∝CV2和延迟∝CV/I。例如,在7nm处,我们预计WL开关能量(扩展数据图12b)将削减约22.4倍,包罗WL电压缩放的2.6倍(1.3V→0.8V)和电容缩放的8.5倍(电容从选择的晶体管、WL驱动器和导线都假定以最小金属间距340nm→40nm举行缩放)。外围电路能量(由神经元读出历程控制)预计将削减42倍,其中5倍来自VDD缩放(1.8V→0.8V)和8.5倍来自更小的寄生电容。MVM脉冲和电荷转移历程消耗的能量与RRAM电导的局限无关,由于RRAM阵列的功耗和确立时间与在它们的乘积中抵消的相同电导因子成比例。详细来说,每个RRAMMAC的能量是EMAC=C4var(Vin),仅受每单元RRAM单元Cpar的寄生电容和驱动输入电压var(Vin)的转变限制。因此,MVM能耗将削减约34倍,其中包罗读取电压缩放(0.5V→0.25V)的4倍,以及更小的寄生电容的8.5倍。总体而言,我们预计将设计从130nm缩小到7nm时,能耗会降低约34倍。

在延迟方面,现在的设计受到神经元积分时间长的限制,主要是由于积分电容器尺寸(104fF)相对较大,为了确保功效准确性和测试差其余神经元事情条件而守旧选择。在更先进的手艺节点上,可以使用更小的电容器尺寸来实现更高的速率。缩小电容器尺寸的主要问题是制造引起的电容器尺寸失配将占总电容的较高比例,从而导致较低的SNR。然而,以前的ADC设计使用的单元电容器尺寸小至50aF。对于更守旧的设计,一项研究注释,在32-nm工艺中,0.45-fF单元电容器的平均尺度误差仅为1.2%。此外,积分时间还取决于晶体管的驱动电流。假设晶体管电流密度(μAμm-1)在VDD缩放后保持相对稳固,而且神经元中的晶体管宽度与接触栅间距(310nm→57nm)成比例,总晶体管驱动电流将削减5.4次。因此,当将Csample从17fF缩放到0.2fF并将Cinteg从104fF缩放到1.22fF时,延迟将提高15.7倍。因此,守旧地说,我们预计在将设计从130纳米手艺扩展到7纳米手艺时,整体EDP至少会提高535倍。扩展数据表2显示,与当今*进的边缘推理加速器相比,这种扩展将使NeuRRAM能够提供更高的能量和单元面积效率。

扩展数据 图 1 |用于 TNSA 和芯片事情模式的外围驱动电路。a 、权重编程模式下驱动电路的设置。b ,在神经元测试模式下。c 、MVM模式下。d ,两个反向流传的 LFSR异或门链天生用于概率采样的伪随机序列的电路图。

扩展数据 图 2 |种种 MVM 数据流偏向及其 CIM 实现。左图,差异 AI 模子中常见的种种 MVM 数据流偏向。中央,种种数据流偏向的通例 CIM 实现。传统设计通常将所有外围电路(例如 ADC)放置在 RRAM 阵列之外。双向和循环 MVM的最终实现会发生面积、延迟和能量方面的开销。右图,可变神经突触 阵列 (TNSA) 在阵列上交织 RRAM 权重和 CMOS 神经元,并以最小的开销支持差其余 MVM 偏向。

扩展数据 图 3 |迭代写入验证 RRAM 编程。a ,增量脉冲写入的流程图-验证手艺将 RRAM 编程到目的模拟电导局限。b , 写入-校验编程的示例序列。c ,在写入-校验编程时代和之后丈量的 RRAM 电导漫衍。每个蓝点代表在写入-验证时代丈量的一个 RRAM 单元。灰色阴影显示 RRAM 电导驰豫导致漫衍从目的值扩展。较深的阴影注释迭代编程有助于缩小漫衍。d ,在初始编程后差异初始电导状态和差异延续时间丈量的电导转变的尺度误差。最初的电导驰豫发生的速率比耐久保留下降的速率更快。e ,电导弛豫的尺度误差随着迭代编程周期的增添而减小。f ,到达电导接受局限所需的 SET/RESET 脉冲数的漫衍。

扩展数据 图 4 |4 个基本的神经元操作,使 MVM 具有多位输入和输出。a 、初始化、预充电采样电容C sample 和输出线 (SLs),以及放电积分电容器C integ 。b ,采样和积分,将SL电压采样到C sample上,然后将电荷积分到C integ上。c 、对照和读出。放大器进入对照器模式以确定集成电压的极性。对照器输出通过外部反馈回路从神经元中写入。d ,电荷削减,电荷在C integ上的加减通过外部反馈回路,取决于存储在锁存器中的值。

扩展数据 图 5 |丈量的 MVM 与理想 MVM 的散点图。图a-d 中的效果是使用相同的 64 × 64 正态漫衍随机矩阵和 1000 个平均漫衍的浮点向量ϵ [-1, 1] 天生的。a ,使用差分输入方案的正向 MVM,输入量化为 4 位,输出为 6 位。b ,使用差分输出方案的反向 MVM。较高的 RMSE 是由于每个 SL 驱动器上需要驱动 128 个 RRAM 单元的电压降更大,而在正向 MVM 时代每个 BL 驱动器驱动 64 个单元。c ,当输入从 4 位 (a) 增添到 6 位时,MVM 均方根误差 (RMSE) 不会削减。这是由于使用较低的输入电压导致更差的信噪比造成的。d ,两相操作通过将输入分成 2 段并划分执行 MVM 来降低 6 位输入的 MVM RMSE,这样就不需要降低输入电压。e - f ,来自 ResNet-20 的 conv15 层的输出。conv15 的权重分为 3 个 CIM 焦点。在 3 个内核 上并行执行 MVM 时(f),层输出显示出比在 3 个内核上顺序执行(e)更高的 RMSE。

扩展数据 图 6 |有和没有模子驱动芯片校准的数据漫衍。左图,当输入是从(从上到下)CIFAR-10 测试集数据、训练集数据和随机统一数据天生时,ResNet-20 最终全毗邻层的输入漫衍。右图,来自 ResNet-20 的最终全毗邻层的输出漫衍。测试集和训练集具有相似的漫衍,而随机平均数据发生显著差其余输出漫衍。为确保在测试时代校准 MVM 输出电压动态局限以占有整个 ADC 输入摆幅,校准数据应来自与测试集数据异常相似的训练集数据。

扩展数据 图 7 | CNN、LSTM 和 RBM 的抗噪训练。a ,推理历程中差异权重噪声水平下CIFAR -10 测试集分类精度的转变。噪声示意为权重**值的分数。差其余曲线代表在差异噪声注入水平下训练的模子。b ,语音下令识别准确度随重量噪声水平的转变。c ,MNIST 图像重修误差随权重噪声水平的转变。d ,在 RBM 推理历程中,通过 Gibbs 采样步骤削减图像重修误差。e ,在没有和有噪声注入的情形下训练时权重漫衍的差异。

扩展数据 图 8|丈量的芯片推理性能。a ,由于硬件不理想导致的 CIFAR-10 训练集精度损失,以及芯片在环渐进微调的每一步的精度恢复。从左到右,每个数据点代表一个新层编程到芯片上。蓝色实线示意在片上执行该层推断时丈量的精度损失。红色虚线示意通过微调后续层丈量的精度恢复。b ,消融研究显示了输入、激活和权重量化以及权重噪声注入对推理错误的影响。

扩展数据 图 9 |种种AI模子的实现。a ,用于 CIFAR-10 分类的 ResNet-20 架构。b ,批量归一化参数在片上映射之前合并为卷积权重和误差。c ,将卷积层的 4 维权重映射到NeuRRAM CIM 焦点的历程示意图。d ,用于谷歌语音下令识其余 LSTM 模子的架构。该模子包罗 4 个并行 LSTM 单元,并凭证 4 个单元的输出总和举行展望。e ,用于 MNIST 图像恢复的 RBM 模子的架构。在推理历程中,MVM 和 Gibbs 采样在可见和隐藏神经元之间往返执行。f ,在NeuRRAM CIM 内核上映射 RBM 的历程。相邻的像素分配给差其余内核,以平衡差异内核的 MVM 输出动态局限。

扩展数据 图 10|使用 RBM 举行芯片丈量的图像恢复。上半部门:随机选择 20% 的像素翻转为互补强度的 MNIST 测试集图像的恢复。下半部门:MNIST 测试集图像的恢复,底部 1/3 的像素被遮挡。

扩展数据 图 11 |种种规模的NeuRRAM测试系统和芯片显微照片。a , NeuRRAM芯片引线连到封装。b ,将封装的NeuRRAM芯片(左)毗邻到现场可编程门阵列(FPGA,右)的丈量板。该板包罗为芯片供电、操作和丈量所需的所有组件。芯片操作不需要外部实验室装备。c ,48 核NeuRRAM芯片的显微照片。d ,单个 CIM 焦点的放大显微照片。e , TNSA内2 × 2小核的放大显微照片。一个神经元电路占用 1270 μm2 ,比 一项ADC 考察中总结的大多数 130-nm ADC 设计小 100多倍。f ,芯片面积细分。

扩展数据 图 12 |能耗、延迟和吞吐量丈量效果。a ,在 MVM 输入阶段(无两相操作)和输出阶段丈量的每次操作的能耗,其中一次乘法累加( MAC) 计为两次操作。b ,差异 MVM 输入和输出位精度下的能耗剖析。在 MVM 时代,输出比输入高 2 位,以解决部门和累加的分外精度要求。c ,执行一个具有 256 × 256 权重矩阵的 MVM 的延迟。d ,峰值盘算吞吐量(以每秒千兆操作为单元)。e ,吞吐量-功率效率(以每瓦兆次运算为单元)。

扩展数据表 1 |完全集成的基于 RRAM 的 CIM 硬件对照

注解:

1. 该表不包罗未讲述详细性能指标的研究。

2. 所有讲述的指标都是为执行 256 × 256 矩阵向量乘法而丈量的。

3. 所有讲述的数字代表阵列行使率为 100% 时的峰值吞吐量/效率。

扩展数据表 2 |与数字 CMOS AI 推理加速器的对照

注解:

1. 将NeuRRAM效率投射到 7 nm 的方式在方式中举行了说明。

2. 数字加速器的能效展望基于 CV 2缩放,其中 C 以最小金属间距缩放,V 调整为 7 nm 的标称 VDD。

3. 数字加速器的面积效率投影基于沿水平和垂直偏向的最小金属间距缩放。

下一篇:制造业大国的汽车出海之路